对于许多应用,如RF记录和回放,电子设备验证和高通道数数据采集都会产生大量的数据。 传统上,示波器、逻辑分析仪和任意波形发生器等台式仪器系统只能实现有限的数据串流。 随着仪器的不断演进,仪器可能具有令人难以置信的快速采样率和高信号带宽,但是仪器与PC之间负责向用户返回数据以便进行处理或存储的连接总线却往往是个瓶颈。 数据通信总线的吞吐量可直接影响仪器带宽接入,进而影响整体测试和测量时间。

随着基于PC的测量硬件不断采用更高性能的数据总线,这些硬件不仅可以更有效地解决现有应用需求,而且还可解决以前无法满足新的应用需求。 PCI Express到PXI Express总线的演进进一步提高了数据传输速率。 从仪器经由控制器到达硬盘的数据串流将仪器的可用内存从百兆字节提高到千兆字节。 利用高带宽PXI Express总线架构,数据能够以足够高的速率实现硬盘,以支持高端仪器。 现在,随着读/写速度和存储容量的提高,数据流可在比以往更长的测试时间周期内实现更快速的采样率。

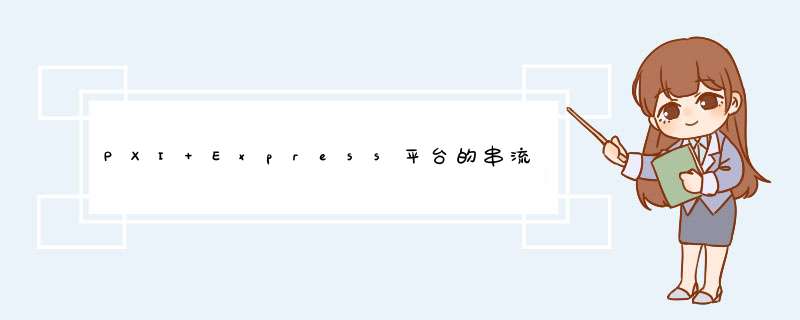

2. 典型的串流架构典型串流架构的主要目标是为了通过仪器高速来回传输数据以便连续生成或采集信号。 执行信号生成任务时,上位机会从内存获取数据,然后通过通信总线传输至仪器。 接着仪器会根据这些数据生成物理信号。 信号采集任务则是反向实现:仪器生成的数据通过总线传输至上位机,最后存储在内存中。 取决于基本组件与总线接口所搭载的技术,很多元件都会给系统带来吞吐量瓶颈,进而降低串流速率。

图1.评估每个系统接口,以便实现最高串流性能来满足应用需求,例如存储和回放已记录的RF数据。

3. 串流架构的发展

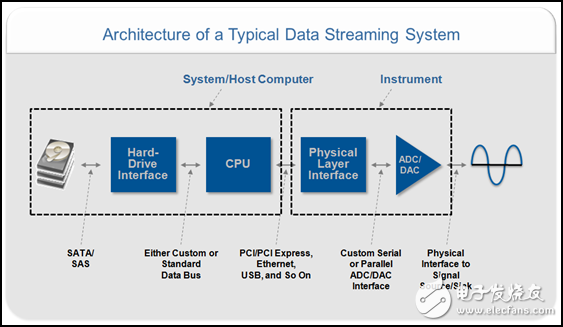

图2.PCI系统的数据流架构,位于PXI嵌入式控制器和机箱之间。

根据规范,理论上PCI总线的最大带宽为132 MB/s,可转换为110 MB/s的实际持续吞吐量。 由于所有的PCI设备仅通过一条链路与主机控制器进行数据通信,因此所有设备都会共享110 MB/s的实际带宽。 因此就PXI系统而言,PXI机箱内的所有模块都会共用PCI总线带宽。 随着PXI仪器的性能不断提高,应用也随之不断演变,而且模块与控制器之间需要传输的数据量也将持续增加。 对于这些应用,PCI总线的吞吐量将很快就不够用。

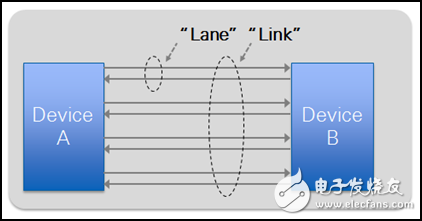

作为PCI总线的进化版,PCI Express保留与PCI的软件兼容性,并将并行总线替换为高速(2.5 Gb/s)串行总线。它借助称为“巷道(lane)”的差分信号线对发送数据,使各条巷道在各个方向上具有250 MB/s的带宽。 多条巷道可组合在一起形成x1(乘一)、x4、x8、x16等典型链路带宽。 x16 Gen1链路可提供4 GB/s的单向带宽。 而且,PCI Express设备不像PCI那样与总线上的所有设备共享带宽,而是具有专用带宽。 因此可使用更多的PXI模块持续在嵌入式控制器来回传输数据。

图3:链路根据组合中的通道数量进行定义,并且标示为“xN”,N代表巷道数量。 例如,PCI Express Gen1巷道支持250 MB/s的速率,而PCI Express Gen2巷道则可支持500 MB/s的速率。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)