d丸飞行速度的测量是武器系统各种运动参数中一项至关重要的内容,它是衡量火炮特性,d药特性和d道特性的一个重要指标。在众多的d丸速度测量系统中.激光光幕区截测速靶以其精度高而独具优势。但采用现成的数据采集卡进行数据采集。不仅成本高,而且易受机箱等环境的限制。介绍了一种以FPGA为核心的数据采集系统.当子d穿过光幕靶时,光电探测器获得d丸过靶信号.FPGA控制A/D转换器进行信号采集并存储。以供后续分析和处理。

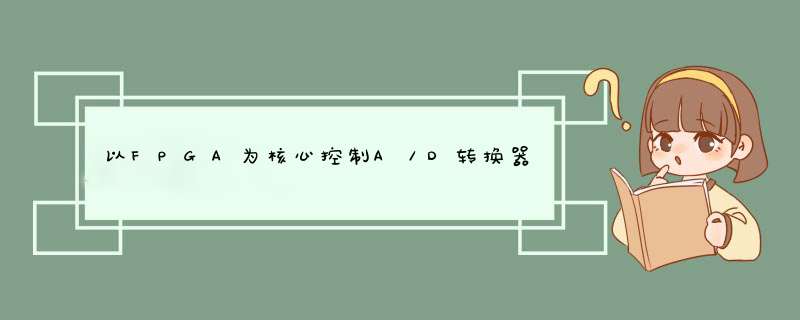

1激光测速靶原理简介激光测速靶就是一种利用光测法测量d丸速度的测试装置。它由初速靶和存速靶组成,初速靶和存速靶又分别由启动靶和停止靶组成。激光测速靶的光源为半导体激光器,激光束经准直、柱面反射镜的扩柬形成人射光幕.d丸依次过靶时.先后遮挡部分入射光线。经原向反射屏反射后由光电探测器获取d丸过靶时的交变信号。信号调理后,由数据采集电路进行采集.最后传输到上位机做数据处理和运算得出子d的飞行速度。

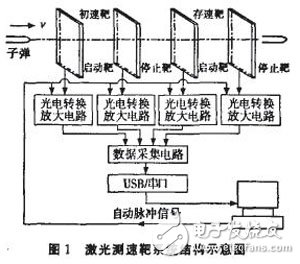

为记录子d在启动靶和停止靶的过靶信号,以启动靶信号为触发源,负延时触发FPGA控制2个A/D转换器同步进行数据采集,将采集到的数据分别存储到SRAM中,然后通过USB依次将SRAM中的数据传输到上位机进行信号的分析和处理。单通道数据采集方案如图2所示。

3.1 FPGA的选择

FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

本系统采用了xilinx公司生产的xC2S50型FPGA。xc2s50是Spartan-Ⅱ系列产品中的一款,它采用了2.5 V电源供电,系统性能可达200 MHz,具有50 OOO个系统门,CLB数量为16×24,LC为1728,BlockRAM容量32 Kbit,拥有176个1/o口。其中XC2S50TQl44的用户可用I/O口为92个,完全能满足系统的需要。

3.2 ADC的选择

步q子d出膛时的初速约为710 mps,d头长约2.5 crn。激光靶激光束宽2 mm,容易算出激光束被子d遮挡的时间为:(25+2)/700 ooo=o.ooo 038 57 s=38.57鼬。也就是说探测器要采集的信号的频率为1/38.57 MHz=25 926.88 Hz。根据奈奎斯特(Nyquist)采样定理,ADC的采样频率应≥5l 853。76 Hz,实际应用中采样频率应≥259 268.8Hz。

AD7482是ADl公司推出的一款12位高速、低功耗逐次逼近式A/D转换器,配有一个并行接口,最高吞吐量可3MsPS。该器件内置一个低噪声、宽带宽采样一保持放大器,可处理40 MHz以上的输入频率。

3.3存储器的选择

可作为固态记录器件的半导体件有多种,主要包括SRAM.DRAM。FRAM,FLASH等几种器件。由于采集的时间短,数据容量小,采用SRAM就能满足应用。N08T1630C1BT是NanoAmp SoluTIons公司~款低功耗512 k×16 bit SRAM,它有19位地址线,16位数据线,逻辑控制简单且易实现。

4主要模块逻辑实现FPGA设计主要包括3个模块部分:A/D转换器控制模块、SRAM控制模块和计时器模块。系统工作过程为:触发信号触发后。FPGA控制A/D转换器开始采集。同时将A/D转换到的数据存储到SRAM中,200 ps后FPGA控制A/D转换器停止采集。等待下一次触发信号的到来。

4.1 A/D转换器控制模块

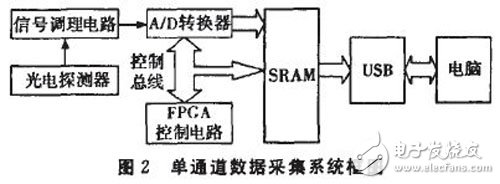

AD7482的主要控制信号有:片选(CS)、读信号(RD)、启动转换(C()NVST)、忙信号(BUSY)。其中,片选(CS)、读信号(RD)控制转换结果读取;启动转换(CoNVST)控制启动转换过程;忙信号(BUSY)标志AD7482正处于转换过程。AD7482满额度工作时的转换时间(conversion TIme)为300 ns.其中.跟踪保持获取时间(track-and—hold acquisiTIonTIme)为70ns,转换结果存取时间为30 ns。实际应用中,2MSPS的采样频率就能满足系统的要求。C()M研控制转换开启关闭,CS和RD连接在一起控制转换结果的存取.编写VHI)L程序.在C她毗usU软件中仿真,仿真结果如图3所示。

图3中,convst跳转为低电平时,AD7482开始模数转换,rd跳转为低电平时,将转换的结果读取到SRAM中。

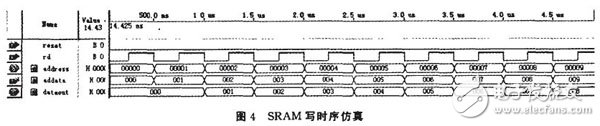

4.2 SRAM控制模块

A/D转换器每转换一次。FPGA控制A/D转换器将转换的结果读取存储到SRAM中。N08T1630ClBT的主要控制信号有:片选(CE)、写使能(WE)、输出使能(oE)、高字节使能(UB)、低字节使能(LB)。N08T1630ClBT的写时序为:确定地址一》拉低CE一》拉低WE一》将要写入的12位数据置于数据线上一》拉高wE。电路中将N08T1630ClBT的片选(CE)端和写使能(wE)端连接到一起,由FPGA发出的rd信号进行控制,即可完成A/D转换结果的数据存储·编写相应的VHDL程序,在QuartusII软件中仿真·仿真结果如图4所示:rd跳转为低电平时,数据写入SRAM,SRAM的地址位加一。

4.3计时器模块

由于启动靶和终止靶之间的距离5是已知的.只要能测出子d通过启动靶和终止靶之间的时间£,就可利用u=s/t测出子d的速度。用VHDL语言编一以启动靶触发信号为启动信号和以终止靶触发信号为停止计数的计时器,便可得出子d通过启动靶和终止靶之间的时间。计数器的编程很简单。在此就不再多作说明。

5.结论通芒翌.激光测速靶数据采集系统的改进,采用FPGA控制A/D转换器来完成数据采集,以代替现成的数据采集卡,具有电路简单、易于扩展、体积小等优点,大大降低了测速靶的成本,进一步增加了系统应用的灵活性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)