通用异步收发器(UART, Universa lA synchronousRece iver Transm itter)是一种应用广泛的短距离串行传输接口, 具有传输线少、成本低、可靠性高等优点。 8250、8251等都是常见的UART 接口芯片, 但专用芯片一般引脚较多, 内含许多辅助模块和一些辅助功能, 在实际使用时往往用不到这些功能, 基本的UART 通信只需要接收和发送两条信号线, 接收与发送是全双工形式, 因此若采用UART 专用芯片, 将会使电路变得复杂, PCB面积增大, 从而导致成本增加, 系统的稳定性和可靠性降低。 由于FPGA 的功能日益强大, 开发周期短、可重复编程等优点也越来越明显, 可以在FPGA 芯片上集成UART 功能模块, 从而简化电路, 缩小PCB 面积, 提高系统可靠性。 此外, 基于FPGA 的设计具有很高的灵活性, 可以方便地进行升级和移植。

1、 UART 控制器的FPGA实现异步收发器的顶层模块由波特率发生器、UART 接收器和UART发送器构成。 UART 发送器的用途是将准备输出的并行数据按照基本UART 帧格式转为TXD 信号串行输出; UART 接收器接收RXD 串行信号, 并将其转化为并行数据, 但串并转换的时钟同发送器一样处理, 收发设备间的时钟是会累计的, 会导致接收数据不正确, 波特率发生器就是专门产生一个远远高于波特率的本地时钟信号对输入RXD 不断采样, 以不断地让接收器与发送器保持同步。

本设计主要分为波特率发生器模块、发送模块和接收模块, 采用的芯片为康欣公司的KX _7C5系列芯片, 其具体型号为EP2C5T144, 具备4608个逻辑宏单元、两个锁相环, 约20万门、约12万RAM bi.t 具体实现方法如下:

1. 1、波特率控制器

波特率控制可有多种方法实现, 常用计数器分频, 或利用片内锁相环控制, 分频较为简单, 但对输入频率有要求, 分频后的频率必须在该波特率下频率偏差允许范围内, 设定较好的输入频率值, 可解决此问题,这样可较少消耗片内资源, 锁相环技术虽然对输入频率没有过高要求, 但定制内部锁相环, 必然耗费较多的片内资源, 本设计出于对片内资源的考虑, 采用了分频方法实现波特率控制器。 波特率发生器实际是一个频率变换器。 可以根据给定的系统时钟和要求的波特率, 通过内部的分频或倍频, 最终得到适宜双方通信的一个时钟频率。 发送器和接收器以该频率为基准, 进行发送和采样接收。

1. 2、接收器

由于串行数据帧和接收时钟是异步的, 由逻辑1转为逻辑0可以被视为一个数据帧的起始位。 然而为了避免毛刺影响, 能够得到正确的起始为信号, 必须要求接收到的起始位在波特率采样过程中至少有一半是属于逻辑0才可以认定接收到的是起始位。 由于内部采样时钟是发送和接收时钟频率的16倍, 所以起始位至少有8个连续采样时钟周期的逻辑0被收到, 才认为起始位接收到, 接着数据位和奇偶校验位将每隔16个采样时钟周期被采样一次(即每一个波特率时钟采样一次)。 如果起始位的确是16个采样时钟周期, 那么接下来数据在每位中点处被采样, 采得的数据进行移位寄存, 当一帧接收完, 把移位接收寄存器中的内容放入接收缓冲寄存器, 同时产生接收完一帧的标志信号。

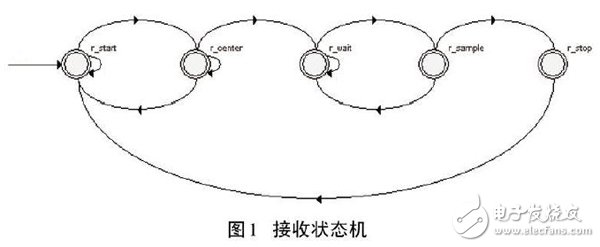

基于UART 的实现原理和通信协议, 本设计采用图1的状态机完成此模块。

接收器共设有5个工作状态: R_START (等待起始位)、R_CENTER (求中点)、R_WA IT (等待采样)、R_SAMPLE (采样)、R_STOP(停止位接收) 。

( 1) R_START状态: 当UART接收器复位后, 接收状态机将处于这一个状态。 在此状态, 状态机一直在等待RXD的电平跳转, 从逻辑1变为逻辑0, 即起始位, 这意味着新的一帧UART数据帧的开始, 一旦起始位被确定, 状态机将被转入R_CENTER状态。

( 2) R_CENTER 状态: 在本状态, 判定起始位是否真实, 通过对采样时钟的个数进行计数( RCNT16为采样时钟个数计数器) , 可以认为保持逻辑0超过1 /2个位时间的信号一定是起始位。

( 3) R_WA IT状态: 当状态机处于这一状态, 等待计满15个采样时钟周期, 在第16个采样时钟周期是进入R_SAMPLE状态进行数据位的采样检测, 同时也判断是否采集的数据位长度已达到数据帧的长度( FRAMELEN ) , 如果到来, 就说明停止位来临了。

( 4) R_SAMPLE 状态: 即数据位采样检测, 完成后无条件状态机转入R_WA IT状态, 等待下次数据位的到来。

( 5) R_STOP状态: 无论停止位是1还是1. 5位, 或是2位, 状态机在R_STOP不具体检测RXD, 只是输出帧接收完毕信号(REC_DONE《 = ‘1’), 停止位后状态机转回到R START状态, 等待下一个帧的起始位。

1. 3、发送器

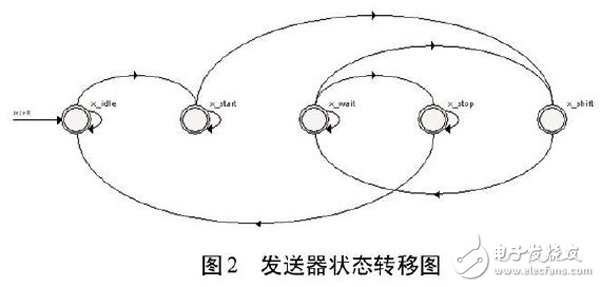

发送器在收到发送命令后, 先发送一个宽度为16个采样周期的起始位, 并且将发送缓冲区数据放入发送移位寄存器, 然后每隔16个采样周期移位寄存器移位输出1个数据, 当数据发送完, 根据需要选择发送停止位的长度(常用长度有0、1、2) , 停止位的宽度同样是16个采样。 发送器只要每隔16个波特率周期输出1个数据即可, 次序遵循1位起始位, 8位数据位和1位停止位。 在本设计中没有校验位。 该模块也用状态机实现, 状态图如图2:

发送器也设以下5个工作状态: X_IDLE (空闲)、X_START (起始位)、X_WA IT (移位等待)、X_SH IFT(移位)、X_STOP(停止) 。

( 1) X_IDLE状态: 当UART 被复位信号RESETL复位后, 状态机将立刻进入这一状态。 在这个状态下, UART的发送器一直在等待一个数据帧发送命令, 当数据帧发送命令到来, 状态转入X_START, 准备发送起始位。

( 2) X_START状态: 在这个状态下, UART的发送器一个位时间宽度的逻辑0 信号至TXD, 即起始位。 紧接着状态机转入X_WA IT 状态。

( 3) X_WA IT状态: 同UART接收状态机中的R_WA IT状态类似。

( 4) X_SH IFT状态: 当状态机处于这一状态时, 实现待发数据的并串转换。 转换完成立即回到X_WA IT状态。

( 5) X_STOP: 停止位发送状态, 当数据帧发送完毕, 状态机转入该状态, 并发送16个采样时钟周期的逻辑1信号, 即1位停止位。 状态机送完停止位后回到X_IDLE状态, 并等待另一个数据帧的发送命令。

2、仿真测试2. 1、 Testbench

通常是这样的代码: 它对输入产生预定的激励, 然后有选择地观察响应, 并检查该响应是否为我们所期望。 功能验证的核心不仅是这个平台, 更在于对被测对象施加了什么样的激励以及在此激励下被测对象的输出是什么。 Testbench与被测对象的关系如图3:

2. 1. 1、为何要写Testbench

( 1)画波形图只能提供极低的功能覆盖率。

( 2)画波形图无法实现验证自动化。

( 3)画波形图难以定位错误。

( 4)画波形图的可重用性和平台移植性极差。

( 5)通过画波形图的验证速度极慢(特别是基于数据帧长度大的通信类设计, 画波形几乎是不可能的)。

2. 1. 2、Testbench的结构

一个好的Testbench结构应该包含两点要求: 层次清晰和具备较好的重用性。 这两点要求之间也有很重要联系: 只有层次清晰的Testbench才是可重用的, 重用性也将使Testbench层次更加清晰。

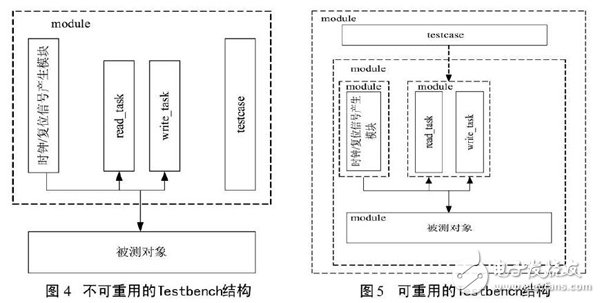

图4是一个不可重用的Testbench结构, 它将所有的处理放在一个模块中, 当进行新的设计时必然不可重用。

图5是一个可重用的Testbench结构, 它将不同处理放在不同的模块, 然后再层次化封装, 当下一次进行类似的设计时, 必然有一部分模块是可以直接调用, 或者只需修改相应参数。

2. 1. 3、本设计的Testbench结构

本设计采用上述可重用的Testbench结构进行了Testbench的设计, 其中Testcase中主要进行了自发自收的测试, 定义了如下的测试序列, 发送数据FF- 00- A5。

2. 2、模块仿真测试

2. 2. 1、波特率控制模块

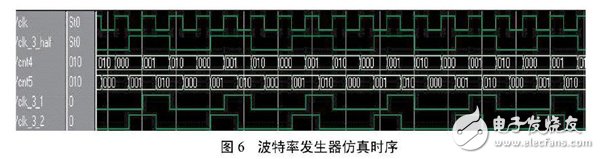

波特率模块主要是一个计数分频器, 输入为高速时钟和波特率因子(即分频系数) , 即可实现任意整数分频, 图6是分频系数为3时的波形仿真图。

2. 2. 2、发送器模块和接收模块

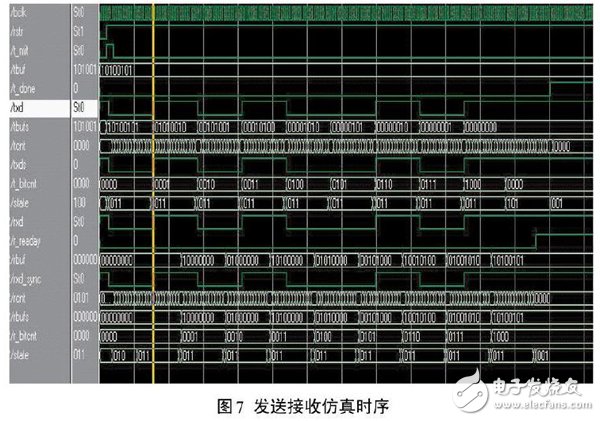

由于可使用自发自收进行测试, 所以发送和接收模块的测试可以同时进行, 设计中的测试数据为A5循环发送。 图7是测试数据的仿真波形图。

分析上图得出结论: 标尺黄线开始, RXD 开始重新接收一帧数据, 同时通过TXD 把tbuf中的数据由低位到高位移位发送。 state为各过程的状态标志, 发送接收状态显示都为011. t b itcnt和r b itcnt分别是发送数据和接收数据计数位, 且发送跟接收数据都准确无误。

2. 3、和PC机通讯的测试

仿真验证功能之后, 将综合后的电路写入FPGA 芯片中, 通过一片RS232转接与PC 机进行串行通信, 上位机使用的是串口调试助手软件, 下位机的结果采用LED显示。 设置好波特率9 600后, PC 机发送的数据可下位机接收, 并由LED显示(字符串除外) , 并可以通过转发回PC 机在串口小助手上显示, 所测数据正确无误。

3、结束语本文完成了UART控制器的设计, 实现了异步串行通讯的基本功能, 并通过简单的串口通讯进行了功能调试。 实际运用中可根据外设和处理器的不同需求, 在其基本功能基础上进行波特率调整、不同帧格式的设置等升级改进, 运用于不同的数字系统。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)