在一类产品发售之前,还没有一种半导体工艺像20 nm节点这样引起这么大的争议。争论在于,节点是否应该等待即将投产的EUV光刻法。它并没有:双模式的布板虽然昂贵而且有局限,但是满足了高分辨率掩膜层的需求。

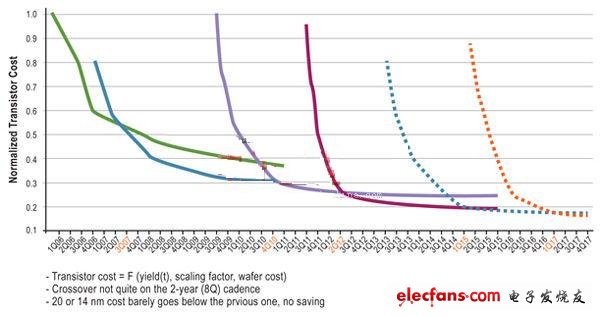

在节点是否需要finFET晶体管上也有争论。Intel、IBM和UMC持赞成态度;三星、TSMC和GLOBALFOUNDRIES则反对。TSMC以前曾有些模棱两可,推进了16 nm finFET半节点计划。而影响最大的是,NVIDIA CEO Jen-Hsun Huang公开质疑整个20 nm节点的经济可行性,他认为,每个晶体管的成本永远不可能低于28 nm。

图1.20 nm技术逐渐成熟起来,其成本可能永远不会低于28 nm技术。

注释:数据基于NVIDIA的公开数

虽然有争论,但是,TSMC发布了其20 nm参考流程。已经着手开始芯片设计。客户已经开始试用测试硅片。现在需要提出的问题是,20 nm芯片系统(SoC)产品代对于系统供应商意味着什么。这一节点也仅仅只是摩尔定律发展的另一个台阶吗?对于SoC用户,它会带来很大的新挑战吗?有没有隐藏的风险?为找到答案,我们与20 nm硅片工程师进行了交流,查阅了最近的会议论文。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)