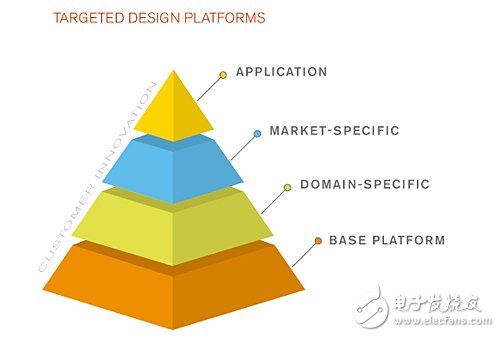

2009年2月Virtex®-6和Spartan®-6系列的隆重发布,标志着赛灵思公司致力于提高FPGA设计效率和增强FPGA易用性的崭新平台方法的开端。与半导体领域内的领先公司所采用的许多平台设计方法相同,赛灵思的目标设计平台 (Targeted Design Platform) 也采用了开放的标准、通用的开发流程以及类似的设计环境,尽量减少任何开发项目中都能遇到的通用工作对设计人员时间的占用,确保他们能集中精力从事创新性的开发工作。

之所以选择了“目标”这个词,是因为每一代新的FPGA都为日益增加的应用提供了更好的解决方案,解决这些应用在嵌入式、数字信号处理或系统方面所面临的需要高带宽通信通道以便处理大量数据的瓶颈问题。其成功之道在于能够充分发挥FPGA内在的并行性、集成存储、DSP和通讯特性的优势。进行系统设计的工程师背景各不相同,分别来自不同的设计领域,他们需要有助于发挥出各自领域专长的的工具和知识产权 (IP)。据此,赛灵思认识到必须推出能够全面支持并可轻松扩展到不同终端应用的参考设计,确保参考设计能真正成为终端应用开发的基础或起点。

每个开发套件都包括了面向Virtex-6或Spartan-6器件的开发板;面向DSP、嵌入式或连接、具有优化设计流程的ISE® 设计套件完整版;经过全面验证的目标参考设计;支持专门特性评估和板上诊断的设计示例和演示;完整的文档资料和说明(包括设置、评估和修改参考设计所需的源代码,可作为终端应用设计的起点);以及所有必需的电源、配置和通信线缆。

我们还提供一系列逐步深入的学习指南,帮助FPGA新手快速启动设计工作。这些学习指南介绍了基本的设计方法,如FPGA编程、工具流程编译步骤、设计方案的创建以及验证等内容。

连接平台

赛灵思的串行和并行连接解决方案能满足实现背板、芯片间或不同产品间系统整合所需要的带宽、电源和成本最高标准要求。利用最新一代Virtex-6和Spartan-6器件,可成功实现最低功耗、最高速串行收发器的设计,并得到业界最广泛的协议支持。此外,内置的PCI Express®和三模以太网MAC块还能节约宝贵的逻辑资源和功耗,同时以更低的成本实现高性能连接。

支持赛灵思 Spartan-6 FPGA和高性能Virtex-6 FPGA系列的两款新型连接套件为赛灵思连接解决方案提供了简单易用的完整开发和演示平台。

处理平台

对习惯于使用RISC或DSP处理器的开发人员来说,转向采用FPGA硬件可能相当困难,他们需要学习一系列新的设计技巧,并对硬件进行一定的了解。对于刚接触FPGA或FPGA处理的开发人员来说,这真是个非常重要的决定,因为有可能会增加潜在的风险,并有可能延长设计周期。

赛灵思面向嵌入式和DSP应用的Spartan-6和Virtex-6 FPGA开发套件专门设计专门用于简化FPGA的推广,使软硬件和算法开发人员能快速启动赛灵思 FPGA片上系统 (SoC) 应用的开发工作。

图2:赛灵思 Virtex-6 FPGA ML605和Spartan-6 FPGA SP605开发板

下面我们将详细介绍2009年12月8日宣布推出的四款开发套件:

赛灵思 Spartan-6 FPGA连接开发套件

赛灵思 Spartan-6 FPGA连接套件采用低成本Spartan-6 LXT器件系列,是一款完整的、简单易用的连接开发和演示平台。作为赛灵思连接目标设计平台,该套件提供了创建高速串行系统和其它开箱即用型连接应用所需的软硬件、IP和目标参考设计。

采用Spartan-6 LXT FPGA的连接套件简化了多协议系统的设计、开发和验证,使设计人员能通过高效、低成本的可编程连接解决方案来实现产品差异化。该套件集成了连接开发所需的关键组件,可加速设计、实施低成本协议桥接,而且对LVDS通信而言提供了效率更高的替代方案,能满足多种不同细分市场的要求。通过提供可扩展的构建块架构以及目标参考设计和业界标准的FMC子卡扩展硬件环境,它还能作为针对市场专用的连接设计平台的起点。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)