以QuartusII13.0EDA软件为例,介绍Verilog文本输入的EDA设计流程。

1.首先在D盘或G盘等新建一个文件夹,用英文字母命名,例如建立文件夹SY1。

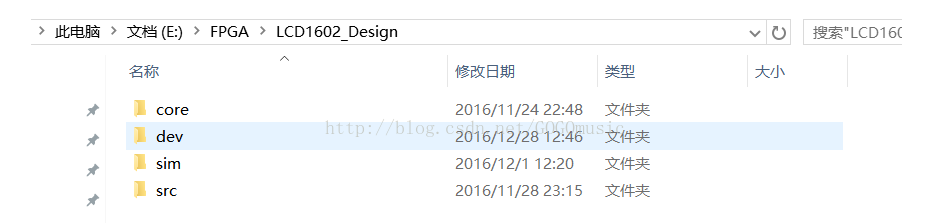

FPGA工程目录 : dev: 工程建立在此文件夹,工程设置

core:IP核保存区

src:用户代码保存区

sim:testbench仿真测试文件

doc:设计参考文档

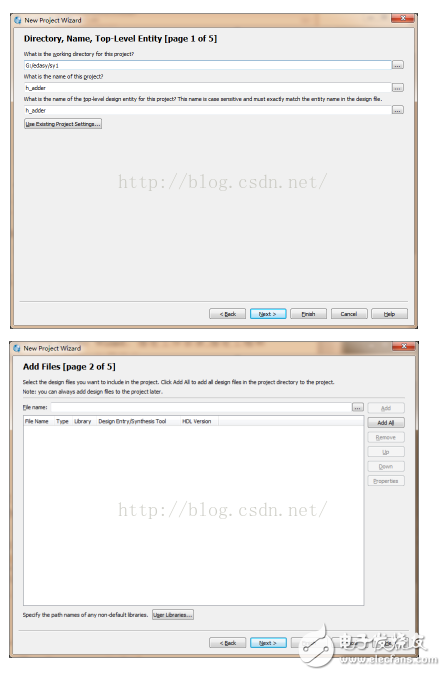

然后打开QuartusII软件,选择File/New Project Wizard,指定工作目录,指定工程和顶层设计实体;注意:工作目录名不能有中文。如图4-3所示。

图4-3 新建工程 图4-4 添加设计文件

2.添加设计文件。将设计文件加入工程中。单击“Next”,如果有已经建立好的Verilog等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL ,.Verilog原理图等)。如果没有直接点击“Next”,等建立好工程后再添加也可,这里我们暂不添加,如图4-4所示。

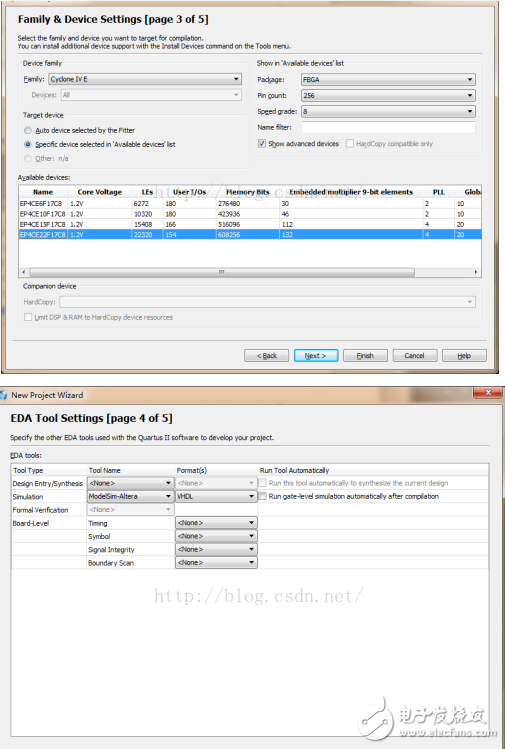

3.选择FPGA器件。EP4CE22F17C8器件选择如下:(Family选择CycloneⅣE,Available device选EP4CE22F17C8,Packge选择FBGA,PinCount 选择256,Speedgrade选择8);EP3C80F484C8器件选择如下:(Family选择CycloneIII,Available device选EP3C80F484C8,Packge选择FBGA,PinCount 选择484,Speedgrade选择8);笔者至今就用过这两种。如图4-5所示,点击“Next”。

图4-5 选择器件 图4-6 选择仿真器

4.选择外部综合器、仿真器和时序分析器。Quartus II支持外部工具, Quartus II 9.1以上版本软件没有自带的仿真工具, simulaTIon选择Modelsim-Altera, Format:Verilog,则采用Modelsim仿真,如图4-6所示,选择完毕后,单击“Next”。

单击“Next”,d出“工程设置统计”窗口,上面列出了工程的相关设置情况。最后单击“Finish”,结束工程设置。

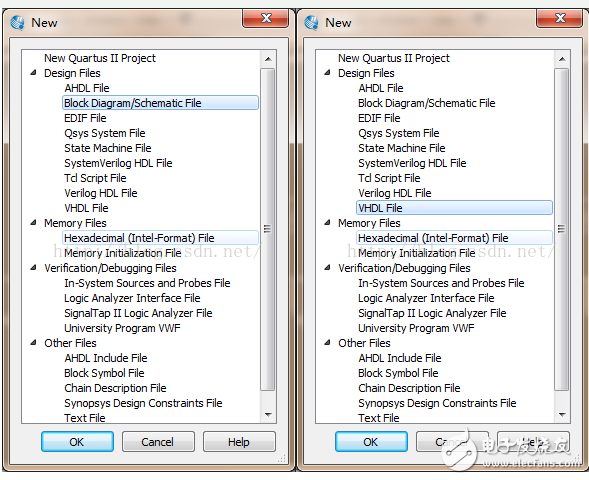

5.新建原理图/文本文件。如果在建立工程时没有添加设计文件,这时需要新建文件。点击“file”点击“new”选择,如果选择原理图输入,选择BlockDiaqram/SchemaTIc File,如图4-7所示。如果选择Verilog文本输入,选择Verilog HDL File,如图4-8。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)