摘要:叙述了L82C37A可编程DMA控制器的主要功能、制造工艺和测试,并对其基本电路及设计方法进行了简要介绍。

1 概述该电路采用2.0μm硅栅CMOS全离子注入工艺制造,集成度为13500管位,芯片面积为25.12mm2,采用DIP 40 PIN 陶瓷封装。

该电路具有以下特点:

与NMOS 82C37A兼容;

具有四个可编程的独立DMA通道,每个通道具有自动初始化能力;

能到存储器到存储器间的传输;

有四种基本工作方式和三种传输方式;

任意扩展DMA通道数;

每个通道有64k地址和64k字节记数空间;

数据最高传输速率可达4MB/秒;

低功耗静态CMOS设计,IDDSB=10μA;

与TTL兼容;

单5V电源工作;

工作频率8MHz;

工作温度范围-55℃~+125℃。

2 逻辑结构和功能 2.1 L82C37A主要功能L82C37A主要功能有以下七点:

(1)该电路有四个独立DMA通道;

(2)每个通道的DMA请求都可分别允许和禁止;

(3)每个通道的DMA请求优先权具有固定方式和循环方式;

(4)每个通道一次传送的最大长度64k字节的数据,可在存储器与外设间进行传送,也可在存储器的两个区间进行传送;

(5)有四种DMA传输方式:①单字节传输方式;②数据块传输方式;③请求传输方式;④ 级连方式。在每种方式下,都能在接收外设的请求信号DREQ后,向外设发送响应信号DACK后就可以占用总线,进行DMA传送。每传送一个字节,修改一次地址指针,当规定传送的字节数送完时,发出终端计数脉冲TC,结束传送或重新初始化;

(6)允许外设用EOP信号结束DMA传送或重新初始化;

(7)L82C37A可以级联,任意扩展通道数。

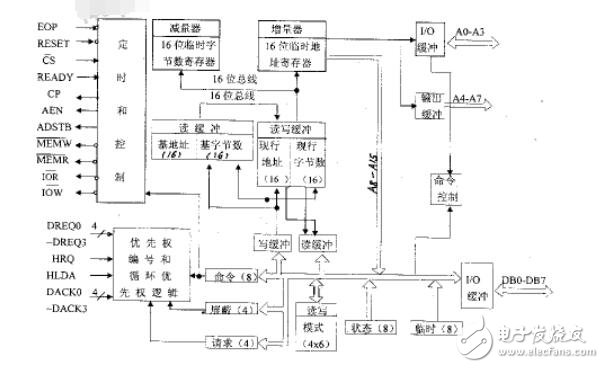

2.2 L82C37A逻辑结构L82C37A的逻辑功能较为复杂,其逻辑框图如图1所示。图中的通道部分只画出了一个通道的情况,即每个通道都有一个基地址寄存器(16位)、基字节数计数器(16位)、现行地址寄存器(16位)和现行字节数计数器(16位),每一个通道都有一个6位的模式寄存器,用以控制不同的工作模式。

图1 L82C37A逻辑框图

L82C37A的结构中包含了三个基本的控制逻辑块。

时序控制逻辑块:根据编程规定的DMA的工作模式,产生包括DMA请求、DMA传送及DMA结束所需要的内部时序和外部信号。

程序命令控制块:对在DMA请求服务之前,CPU编程对给定的命令字和模式控制字进行译码,以确定DMA服务的类型。

优先权编码逻辑:对同时有请求的通道进行优先权编码,确定哪个通道的优先权最高,优先权可以是固定的,也可以是循环的。

另外,L82C37A的数据引线都有三态缓冲器,因而可以占用也可以释放总线。

2.3 L82C37A的工作周期L82C37A有两种主要的工作周期,即空闲周期和有效周期,每一个周期由若干个时钟周期组成。

(1)空闲周期

L82C37A在完成了一个DMA服务之后,若没有新的DMA请求,或在主清零或硬件复位后,将进入空闲周期执行SI状态。在每个时钟周期它都要对通道的请求线DREQ进行采样,在没收到DREQ前,它将始终处于SI态。

在此状态中,CPU可以查询其状态或对其进行编程。若 ,则CPU可以对其进行读写 *** 作,可以对其基地址、基字节数、当前地址、当前字节数等寄存器进行读/写。此时,需通过数据总线和地址总线以及

,则CPU可以对其进行读写 *** 作,可以对其基地址、基字节数、当前地址、当前字节数等寄存器进行读/写。此时,需通过数据总线和地址总线以及 和来选择寄存器并改写数据。由于这四组寄存器均为16位,而数据总线是8位的,则由内部高/低位寄存器控制,将数据分成高8位和低8位,分两次写。另外还有些软件命令,不通过数据总线,仅由地址A0-A3和

和来选择寄存器并改写数据。由于这四组寄存器均为16位,而数据总线是8位的,则由内部高/低位寄存器控制,将数据分成高8位和低8位,分两次写。另外还有些软件命令,不通过数据总线,仅由地址A0-A3和 等信号的译码来设置。

等信号的译码来设置。

(2)有效周期

当外设或CPU发出DMA请求时,将跳出SI状态进入DMA服务的第一状态S0。此时,虽收到SREQ并发出HRQ,但在收到CPU返回HLDA信号后,L82C37A才进入由S1-S3组成的工作状态,若外设的工作速度较慢,DMA传送不能在S4状态之前完成时,则可用READY线在S2或S3与S4之间插入SW状态,直到本次传输结束。SW状态是等待周期,主要是为适应慢速外设,以延长传输时间。

在存储器至存储器传输时,要作存储器读和写 *** 作,所以每一次传输需要8个时钟周期,其中4个周期S11-S14完成存储器读,另外4个周期S21-S24完成存储器写 *** 作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)