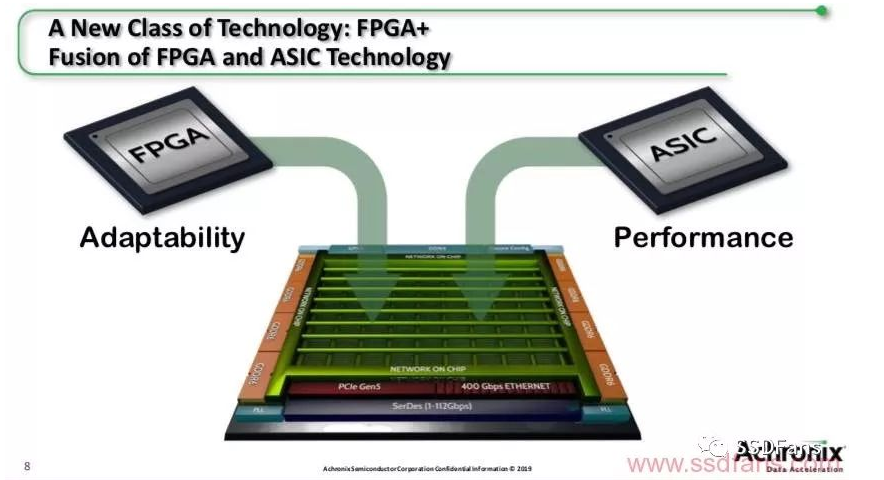

为什么当前的FPGA设备看起来像原来的电话系统,非常像工作人员使用电线和插头连接呼叫的交换机?Achronix认为现在是时候放弃Switch Blocks并采用新方法了。他们的目的是提高FPGA在机器学习应用中的适用性,这意味着它们具有更多类似ASIC的性能特征。然而,除了更新数据在芯片上的移动方式之外,还有很多其他改变。

Achronix已经确定了FPGA需要改进的三个方面,从而使它们成为实现机器学习应用程序的首选。当然,他们需要保持其标志性的灵活性和适应性。高效数据加速的三个架构要求是计算性能、数据移动和内存层次结构。Achronix退后一步,分别研究每个元素,以便重新创建在机器学习时代可以更好工作的FPGA。因此他们研究出来了新Speedster 7t。他们的目标是打破降低FPGA效率的历史瓶颈。他们将其称为FPGA +。

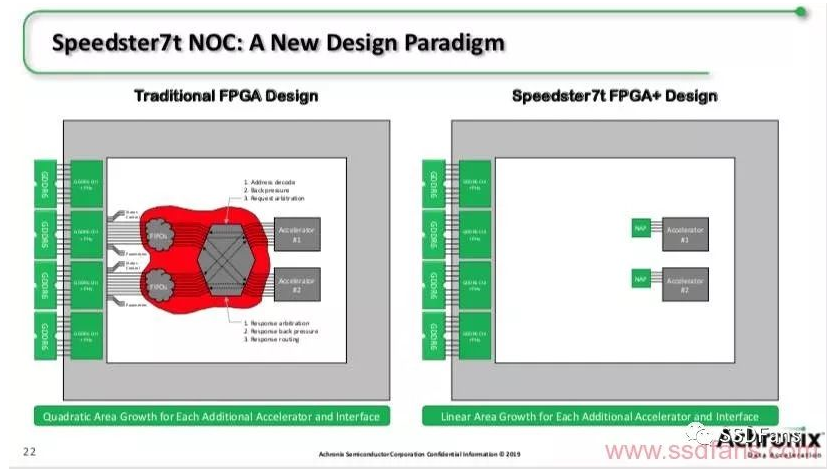

这些新芯片基于台积电的7nm节点,并进行了多项重要创新。就像我们所有的电话呼叫都采用分组技术进行路由一样,Achronix的Speedster 7t将使用二维阵列片上网络(NoC),在计算元件、存储器和接口之间移动数据。NoC由主从网络接入点(NAP)网格组成。每行或列的运行速度为256b @ 2.0Gbps,组合为512 Gbps。这使设备级带宽在20Tbps的范围内。

NoC支持特定的连接模式(AXI)、以太网数据包、无包数据流和FPGA内部连接的NAP to NAP。这样做的一个好处是,可以使用NoC将数据从PCIe预加载到内存中,不需要处理内核的干预。另一个优点是,网络结构消除了放置连接逻辑单元时的压力,这是造成堵塞和层次规划问题的主要原因。

NoC还允许Achronix Speedster 7t支持400G *** 作。Speedster 7t无需在724 MHz运行1000位总线,它可以支持4条并行256位总线,运行频率为506MHz,可以减轻吞吐量的压力。当需要进行深度标头检测时,这一点尤其有用。

对于外设接口,Achronix使用的方法是提供一个高度可扩展的SerDes,运行频率可以从1到112Gbps,以支持PCIe和以太网,每台设备上最多可以包含72个。对于以太网,它们可以运行4x 100Gbps或8x 50Gbps。还支持低速率的以太网连接以实现后向兼容。它们支持PCIe Gen5,每个端口高达512 Gbps,每个设备有两个端口。

当我们查看计算体系结构时,就会发现它们体系结构的真正优势。他们没有单独的DSP LUT和内存块,而是将它们组合成机器学习处理器(MLP)。这样可以立即释放FPGA路由上的带宽。这三个元素在机器学习应用程序中经常一起使用,因此将它们组合在一起对于它们的体系结构来说是一个很大的优势。

AI和ML算法都对数学精度有很高的要求。有时使用较大的浮点数精度,有时也会使用低精度整数,谷歌甚至有自己的Bfloat精度。为了适应这种多样性,Achronix开发了可分离的浮点数和整数MAC。对多种数字格式的支持提供了对MAC资源的高利用率。MLP还包括72Kbit RAM块、内存和 *** 作数级联功能。

对于AI和ML应用程序,本地内存很重要,对系统RAM来说也是如此。Achronix决定在他们的Speedster 7t系列上使用GDDR6。可以实现更低的成本、更灵活的系统设计和极高的带宽。当然,DDR4也可以用于要求较低的存储需求。GDDR6的使用允许每个设计调整它们的内存需求,而不是依赖于与可编程设备配置在同一包中的内存。Speedster 7t支持多达8个设备,吞吐量为4 Tbps。

回过头来看,FPGA的这种演变就像老式的有线台式电话演变成高度连接和集成的通信设备一样。关键在于,这种创新水平将使最终产品能力出现不可预见的进步。根据Achronix Speedster 7t公告,他们的设计工具已经准备就绪。

责任编辑:ct

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)