1 概述

时分复用是当前同步通信系统中用以提高数据传输效率的常用方法。例如第2代移动通信GSM系统,光同步传输网SDH等都是使用时分复用的例子。在现代通信设备的研发中,常常会遇到高速背板通信、多协议接口、网络管理信令通道等需要同时处理多个同步通信接口数据的情况。本文介绍了一种采用MPC8280处理器芯片内部的多通道通信控制单元,来处理多个同步通信接口数据的方法。

MPC8280是飞思卡尔公司PowerQUICC II产品线的较新成员。它采用0.13 μm工艺制造。内核、I/O的供电电压分别为1.5 V、3.3 V。MPC8280相比该公司的MPC8260,制造工艺和工作频率均有所提升,但因为核心电压下降,功耗反而下降。而且,MPC8280片内的DPRAM(双口静态存储器)容量增加了一倍,此外还增加了PCI和USB。

MPC8280芯片由主内核、SIU、CPM等3个主要功能模块组成,如图1所示。MPC8280的处理器主内核称为G2_LE,它是一种PowerPC架构的多级流水线超标量处理器。MPC8280内核运行频率为16*50 MHz。SIU模块主要负责60x总线控制、PCI桥及时钟产生。CPM模块负责处理通信事务,即处理SCC、SMC、FCC、MCC、USB、SPI、I2C等通信控制单元收发数据。本文所述的多通道HDLC控制器即采用CPM下的MCC(多通道控制器)通信控制单元来实现。

MPC8280片内集成的静态存储器包括DPRAM、全局配置寄存器、SI RAM(串行接口路由表配置空间)。其中,第1块32 KB的数据DPRAM空间被等分成16个bank(存储空间块)。CPM中的通信控制单元除了使用全局配置寄存器进行最基本的参数配置外,还须使用参数配置存储区块进一步配置。一般CPM中每个通信控制单元都有2个参数配置存储区块,参数配置存储区块均定位在DPRAM中的指定地址。SI RAM主要用于配置TSA(时隙分配器)的路由表。

2 SI(TSA)的设计

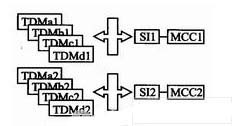

MCC总是和SI(串行接口)配合使用(因为MCC只是数据处理单元,不负责通信数据与MPC8280引脚的交互),因此,只有SI配置好,MCC单元才能正常工作。每个MCC仅与1个SI相关联,而且,MCC1只允许连接到SI1,MCC2只允许连接到SI2。

MPC8280片内含2个SI,每个SI最多可控制4个TDM(时分复用)口。每个TDM口均拥有各自独立的收发帧同步脉冲、收发时钟引脚。时钟的同步边沿、时钟倍频(1×或2×时钟模式)、帧同步信号的超前时钟位数可编程控制。SI与MCC的关系如图2所示。

图2 SI与MCC的关系

TSA的主要工作是数据选路,即将CPM内各个通信控制单元的I/O数据以比特或字节为单位输送到TDM口上。换句话说,TSA相当于MPC8280的CPM模块中各通信控制单元(MCC、SCC、SMC、FCC等)进行TDMA(时分复用)的功能模块,对TSA的编程与后端的通信控制单元无关。TSA根据由SI RAM构造的路由表执行选路。

SI自身没有缓存,它直接与后端各通信控制单元的FIFO相连;SI在时钟的驱动下,按照路由表的配置,将接收到的帧比特流分别送到各指定通信控制单元的FIFO中,以及将各指定通信控制单元的FIFO中的数据输出到TDM口的引脚上,并与各通信控制单元的BD(缓冲区描述符)表和中断交互,完成通信任务。

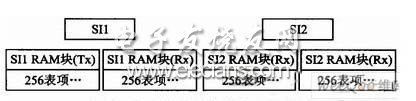

程序员通过对SI RAM块编程来完成路由表的构建。每个SI包含2个SI RAM块,分别用于设计发送和接收的路由表,这样MPC8280内部的2个SI模块总共包含4个SI RAM块。每块由SI RAM构造的路由表包括256条表项,每条表项长度是2字节,每条表项最多可控制8个字节串行流数据的分配,所以1个SI模块支持的最长一帧的长度可达256×8×8=16 384比特。路由表表项的内容就是指定将TDM口上通过1~8个比特或字节的同步数据流分配给MCC、SCC、SMC、FCC等通信控制单元。最后一条表项必须激活路由表的结束标记,告诉TSA已处理完一帧,请等待下一个帧同步信号的到来。

如图3所示,每块SI RAM(内含256条表项)等分为4个bank,即每个TDM口均各有1个bank一一对应;每个bank可以被程序员指派为对应不同的TDM口(但不允许将两个TDM口对应到同一个bank上)。这样,TDM口的串行数据流在指定bank的SI RAM表项的控制下被分别送往指定的通信控制单元进行处理。一个bank的长度可由设计人员自由设定(路由表有首尾标志),这是因为不同的应用,每一帧的比特数目并不一定相同;路由表即精确地确定了每一个TDM口帧流的比特数目。显然,一个帧流必须由多少条表项来处理也可以计算出来,即帧流总比特数/每表项处理的比特数。注意,路由表的表项数目必须是偶数,因此在编程时,如果的确是只有一条表项,那么就还必须再补上一条内容为空的表项。

图3 SI RAM块的组成与对应结构

此外,因为TDM口的接收、发送分别由2个SI RAM块实施控制,所以TDM口发送和接收的比特流的分配可以任意设计,甚至允许将不连续的比特流都分配到一个通信控制单元,也允许一个通信控制单元从某一个TDM接收,而从另一个TDM发送。

3 MCC的标准通道设计

一个MCC的数据是在特定SI控制的4个TDM口上传输;每个MCC可以支持128条时分复用通道(见图4),用来传输HDLC、透明通道,或7号信令通道数据。本文的设计是用MCC实现多通道HDLC通信协议。MCC的数据流可通过TSA的桥接直接送入MCC相应通道的FIFO处理。每个MCC可分解成4个子模块,每个子模块(包含32条通道)对应到1个TDM口上,即处理不同的物理TDM口的数据。MCC中的每个通道的工作模式均可独立设置,收发关系也可以独立映射;支持全局环回和基于单个通道的独立环回。

图4 TDM口与MCC通道的对应关系

每个MCC中包含128个功能完全相同的通道,每个通道都有一套配置寄存器,这些寄存器功能相同,并依靠通道号进行索引寻址,进而初始化。

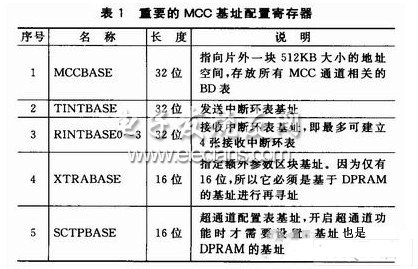

MCC的初始化遵循先全局、后通道的顺序。MCC的全局参数寄存器定位在DPRAM(bank 9)中,占用128字节,该寄存器组相对DPRAM基地址的偏移量为0x8800。在全局参数设置里比较重要的、将影响各通道配置寄存器空间寻址的地址索引寄存器如表1所列。

每个通道都有64字节的专用参数寄存器。采用“DPRAM基址+64×通道号”的方式计算出指定通道的专用参数寄存器组的基址。

每个通道还有8字节的额外参数寄存器,采用“DPRAM基址+8×通道号”的方式计算出指定通道的额外参数寄存器组的基址。该区块的主要内容包括:TBASE(16位,发送BD表首地址计算元素);RBASE(16位,接收BD表首地址计算元素)。

BD表通常放在片外内存中。1个MCC包含128条通道,每条通道都有自己的BD表,所有128条通道的BD表集中连续地存放在一个512 KB的段中。在这个空间内寻址某个通道对应的BD表的基地址的计算方法是:MCCBASE+8×RBASE(接收),MCCBASE+8×TBASE(发送)。接收和发送BD表都是一个环形队形,接收BD表至少须含2条表项,发送BD表至少须含1条表项。编程时,构造结构数组,可以把TBASE、RBASE设计成和通道号对应的数组索引。

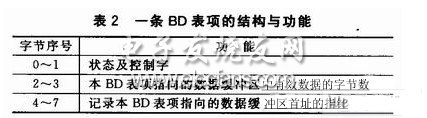

每条BD表项有8个字节,如表2所列。

环形队列结构的中断表也是放在片外内存中。发送中断对应一张表,基地址为TINTBASE;接收中断对应1~4张表,基地址分别为RINT-BASE0~RINTBASE3。中断表的长度完全由用户确定,但最少至少包括2条表项。每条中断表项长度为4字节,记录了中断表项是否有效、中断标志以及触发中断的通道号。

4 MCC的超通道模式设计

工作于超通道模式下的MCC要求SI必须以字节为选路单位。通过“超通道”这个技术将原来分属于几个通道的FIFO聚合成1个更大的FIF-O,传输大容量的同步数据流。聚合的方法是在SI RAM中指定某几个MCCchannel的通道号属于一个超通道,也就是说,为使MCC工作在超通道模式下,必须完成SI RAM和超通道表的初始化。

超通道表用于表示哪几个通道的FIFO共享指定通道的控制参数。例如:160、161、162等3个标准通道组成1个超通道,且由160号通道的控制寄存器来控制该超通道的行为,那么就在超通道表表项中填入“160”。

超通道表仅用于发送控制,而接收不需要构造超通道表。接收的编程比较简单,既不需要设超通道,也比较直接,需要由某个通道处理的数据,直接在SI RAM里打开相应的通道接收即可。

5 中断模型

MCC的中断响应采用两级中断模型:第一级为全局中断状态标志寄存器MCCE,第二级为中断环表。MPC8280*有5个中断环表为MCC通道中断提供中断标志服务:1个用于发送,4个用于接收。中断环表是所有通道共用的。每个通道初始化时必须指定它使用哪个接收中断表来上报接收中断,利用这个特性可以设计出带优先级的中断响应机制。

注意:因为是环表,所以环表内最后一条表项的Wrap位必须置1,环表内的其他表项必须全部置成O。

每当有MCC通道触发中断,MPC8280的CPM模块将会向中断环表中当前空表项位置写入一条表项,并将该表项的“V”有效标志位置1,表示已经收到一次中断,等待用户响应和处理。并且给表项指针加1以指向下一条空表项(当指针到达环表的最后一条时,则CPM模块自动将中断环表的基地址的值重新装入表项指针寄存器,使CPM下一次写入的位置重新定位到中断环表的顶部)。

注意:如果中断屏蔽寄存器INTMSK中设置了一些屏蔽事件,则当这些事件发生时,CPM不会向中断环表写入表项,自然也不会触发全局中断状态标志寄存器MCCE。

用户ISR代码响应MCC中断,访问中断环表表项时,应首先清除“V”标志,然后再处理具体中断请求,并在退出中断服务程序前清除MCCE寄存器的中断标志。程序员应该根据系统的实际情况决定是在进入MCC中断服务程序后将所有中断环表中的中断事件处理完才退出,还是仅处理中断环表一项中断请求后即退出中断服务程序,这需要程序员基于中断响应时间以及不影响其他程序代码运行作综合考虑。

6 实际调试

环回测试是测试通信硬件本身是否正常的重要手段。MPC8280各通信处理单元自身都有环回控制位,例如,SCCHDLC的环回控制在GSMR_L寄存器中设置;MCC的单个通道的环回控制在SI RAM里设置。单个TDM口也可以自环,在SIxMR寄存器里设置。因此,可以通过对MCC的单个通道的自环,以及单个TDM口的自环来测试驱动程序写得是否正确。在这个测试中,MPC8280的TDM口由片外时钟和帧同步脉冲驱动。注意:测试前必须先用示波器确认TDM口引脚上的时钟的频率、波形符合硬件设计要求。另外应当仔细选择MPC8280和外部交换芯片的时钟边缘关系,以免时钟同步异常导致数据判决出错。

初始化代码完成以后,应利用shell工具或其他观察手段检查初始化代码对相关寄存器的写入符合设计目标。不要因为粗心大意写错了寄存器值而无法获得正确结果。因为MCC的工作必须在SI模块的配合下完成,可以将SI模块和MCC分开调试。假如有已经调试完成的SCC(SMC也可以)通信单元的驱动程序,就可以将SCC的数据流从I/O脚定向到SI模块上,如图5所示。测试SCC经过SI模块进行环回是否正常,可以测试SI模块的驱动程序是否正确。测试好SI模块的驱动程序后,再将SCC的驱动程序替换成MCC的驱动程序,即可比较容易地采用相同的模型对MCC驱动程序进行测试了。注意MCC工作在标准模式和超通道模式下时对SI RAM的路由表初始化稍有不同。

图5 SCC1经过SI模块进行环回测试

7 小结

MPC8280是一种功耗低、通信处理能力强的处理器,利用MPC8280内部的多通道控制器的大通信容量通信能力,可以比较容易地设计出信令通道、数据通道、协议转换器等应用。本文介绍了MPC8280内部的多通道控制器的通信原理及调试方法,希望对有相关应用需求的科研人员有所帮助。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)