随着电子技术的飞速发展, 存储器的种类日益繁多,每一种存储器都有其独有的 *** 作时序,为了提高存储器芯片的测试效率,一种多功能存储器芯片的测试系统应运而生。本文提出了一种多功能存储器芯片的测试系统硬件设计与实现,对各种数据位宽的多种存储器芯片(SRAM、MRAM、NOR FALSH、NAND FLASH、EEPROM等)进行了详细的结口电路设计(如何挂载到NIOSII的总线上),最终解决了不同数据位宽的多种存储器的同平台测试解决方案,并详细地设计了各结口的硬件实现方法。

引言随着电子技术的飞速发展,存储器类芯片的品种越来越多,其 *** 作方式完全不一样,因此要测试其中一类存储器类芯片就会有一种专用的存储器芯片测试仪。本文设计的多种存储器芯片测试系统是能够对SRAM、Nand FLASH、Nor FLASH、MRAM、EEPROM等多种存储器芯片进行功能测试,而且每一类又可兼容8位、16位、32位、40位等不同宽度的数据总线,如果针对每一种产品都单独设计一个测试平台,其测试 *** 作的复杂程度是可想而知的。为达到简化测试步骤、减小测试的复杂度、提高测试效率、降低测试成本,特设计一种多功能的存储器类芯片测试系统,实现在同一平台下完成所有上述存储器芯片的方便快捷地测试。

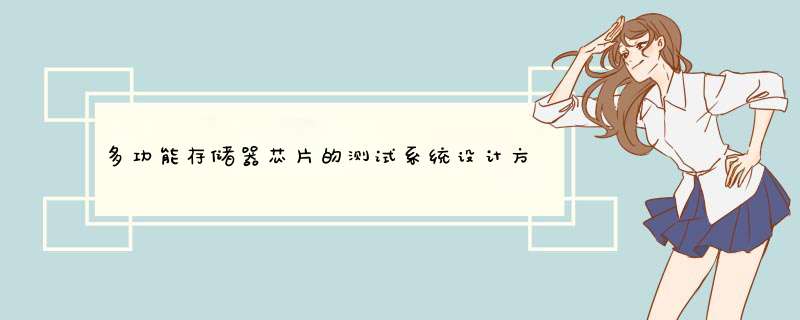

设计原理此设计方案根据上述各种存储器独自的读写时序访问特性,通过FPGA的灵活编程特性,适当地调整NIOSII的外部总线时序,最终实现基于NIOSII的外部总线访问各种存储器读写时序的精确 *** 作。如图2-1。通过FPGA自定义一个可以挂载所有存储器芯片的总线接口-ABUS,如表1。而且在同一个接口上能够自动识别各种接入的被测试存储器芯片,它们通过类别输入信号(CLAS)来区分,每一种存储器芯片对应一种独特的 *** 作时序。下面是几种存储器芯片的接口连接方式及信号描述。其它的存储器芯片都可以用类似的接法挂载到ABUS总线上,最终完成测试。

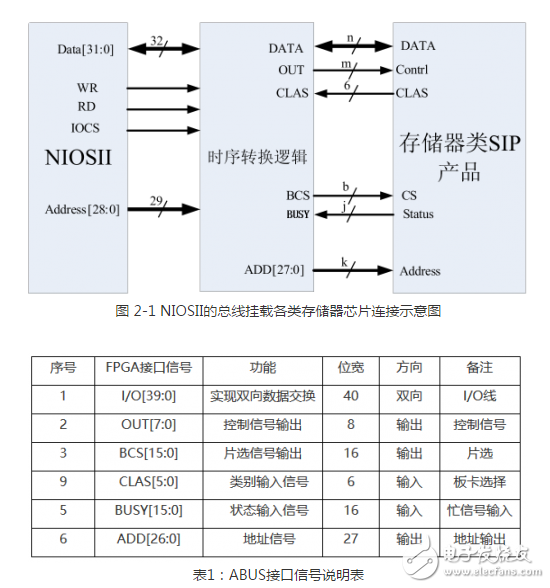

如图2-2所示,40位NAND FLASH与NIOSII 通过ABUS(FPGA)桥接,把外部总线的时序完全转换成NAND FLASH的 *** 作时序。40位NAND FLASH芯片品由五个独立的8位NAND FLASH芯片拼接构成。5个8位器件的外部IO口拼接成40位的外部IO口,而各自的控制线(NCLE,NALE,NRE,NWE)连接在一起构成一组控制线(NCLE,NALE,NRE,NWE),片选相互独立引出成NCS0-NCS9,忙信号独立引出为R/B0-R/B9。

如表2,详述了40位NAND FLASH与ABUS的连接关系。

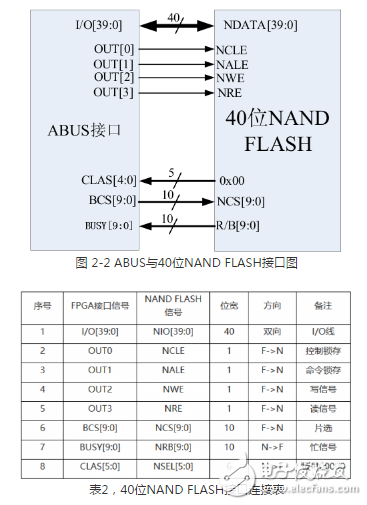

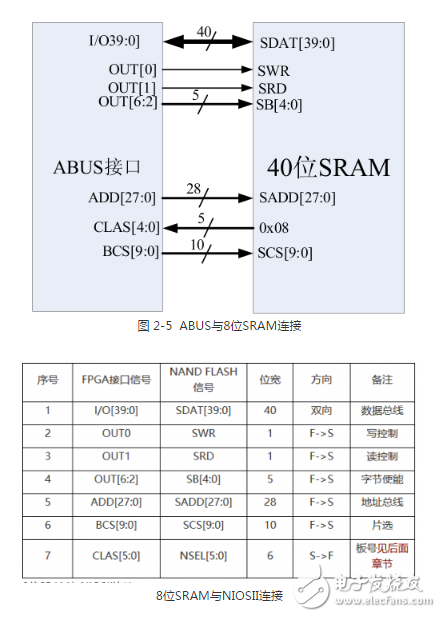

40位SRM模块与NIOSII通过ABUS连接,实现正确的时序读写 *** 作。测试时,一次只测试8位,分5次完成所有空间的测试。如图2-4。表4是详细的信号连接说明。

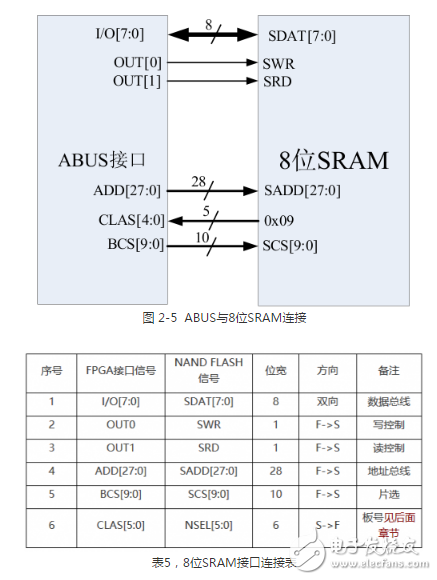

8位SRM模块与NIOSII通过ABUS(FPGA)连接,实现正确的时序读写 *** 作。如图2-5。表5是信号连接说明。

8位SRM模块与NIOSII通过ABUS(FPGA)连接,实现正确的时序读写 *** 作。如图2-5。表5是信号连接说明。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)