1 引 言

目前,实现微电路最常用的技术是使用MOS晶体管。随着科学技术的发展,集成电路的集成密度不断地在提高,MOS晶体管器件的尺寸也逐年缩小, 当MOS管的沟道长度小到一定值之后,出现的短沟道效应将对器件的特性产生影响,使其偏离传统长沟道MOS管的特性

VHDL2AMS(Analog andMixed Signal)是一种高层次的混合信号硬件描述语言,它不仅支持对模拟系统的建模和仿真,而且支持对离散系统及数字模拟混合系统的建模和仿真。它对电路系统的描述既可以采用结构描述,也可以采用行为描述,即只需要描述模型的行为,而不需要声明模型是如何实现的。

2 工作原理

当MOS管沟道缩短到一定程度,就会出现短沟道效应,其主要表现在MOS管沟道中的载流子出现速度饱和现象。在MOS管沟道较长、电场较小的情况下,载流子的速度正比于电场,即载流子的迁移率是个常数。然而在沟道电场强度很高情况下,载流子的速度将由于散射效应而趋于饱和。载流子速度v与电场的关系可用以下关系式来近似:

其中μn 是迁移率, E是沟道水平方向的电场, Ec是速度饱和发生时的临界电场。沟道水平方向的电场取决于UDS /L,对于短沟道MOS管,由于沟道长度L 比长沟道MOS管小得多,因此水平方向的电场也相应大得多,随着漏源电压UDS的增加,很快就可以达到饱和点。因此在分析MOS管特性时,考虑到速度饱和效应,就不能沿用传统长沟道MOS管的电流、电压关系式,需要对其加以修正。

在线性区,漏极电流的公式原来为

其中ID 为漏极电流, kp 为跨导系数,W 为沟道宽度, L 为沟道长度, UT 为阈值电压, UGS和UDS分别是栅极电压和漏极电压。

对于短沟道MOS管,应该修正为

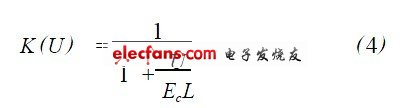

其中, K (UDS ) 因子考虑了速度饱和的因素。K(U)定义为:

UDS /L 可以理解为沟道中水平方向的平均电场,对于长沟道MOS管,由于L 较大, UDS /L 比Ec 小得多,因此K (UDS ) 接近于1, 而对于短沟道MOS 管,K (UDS )通常小于1,因此产生的漏极电流要比通常电流公式计算的值要小。在饱和区,漏极电流的公式原来为

其中, K (UGS - UT )因子考虑了速度饱和的因素。在(UGS - UT ) /LEc 比1大得多的情况下, ID 与(UGS -UT )不再是长沟道MOS管中的平方关系,而接近于线性关系。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)