引言

本文讨论使用分立器件进行电源时序控制的优缺点,同时介绍利用ADP5134内部精密使能引脚实现时序控制的一种简单而有效的方法ADP5134内置2个1.2-A 降压调节器与2个300-mA LDO。同时,本文还列出一系列IC,可用于要求更高精度、更灵活时序控制的应用。

图1 所示为一种要求多个供电轨的应用。这些供电轨为内核电源(VCCINT)、I/O 电源(VCCO)、辅助电源(VCCAUX)和系统存储器电源。

图1. 处理器和FPGA 的典型供电方法

举例来说,Xilinx Spartan-3AFPGA 具有一个内置上电复位电路,可确保在所有电源均达到其阈值后才允许对器件进行配置。这样有助于降低电源时序控制要求,但为了实现最小浪涌电流电平并遵循连接至FPGA 的电路时序控制要求,供电轨应当按以下序列上电VCC_INT → VCC_AUX→ VCCO。请注意:有些应用要求采用特定序列,因此,务必阅读数据手册的电源要求部分。

使用无源延迟网络简化电源时序控制

实现电源时序控制的一种简单的方法就是利用电阻、电容、二极管等无源元件,延迟进入调节器使能引脚的信号,如图2 所示。当开关闭合时,D1导电,而D2仍保持断开。电容C1充电,而EN2处的电压根据R1和C1确定的速率上升。当开关断开时,电容C1通过R2、D2和RPULL向地放电。EN2处的电压以R2、RPULL和C2确定的速率下降。更改R1和R2的值会改变充放电时间,从而设置调节器的开启和关闭时间。

图2. 利用电阻、电容和二极管实现电源时序控制的简单方法

该方法可用于不要求采用精密时序控制的应用,以及只需延迟信号即可并可能只要求采用外部R和C的部分应用。对于标准调节器,采用这种方法的缺点在于,使能引脚的逻辑阈值可能因为电压和温度而存在很大的差异。此外,电压斜坡中的延迟取决于电阻和电容值及容差。典型的X5R电容在–55°C至 +85°C温度范围内的变化幅度约为±15%,由于直流偏置效应还会出现±10%的变化,从而使时序控制变得不精确,有时还会变得不可靠。

精密使能轻松实现时序控制

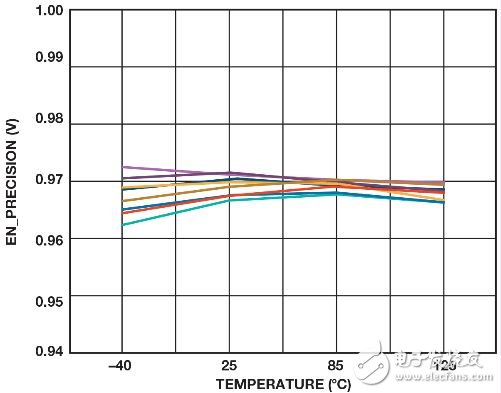

为了获得稳定的阈值电平以实现精密时序控制,大多数调节器都要求采用一个外部基准电压源。ADP5134通过集成精密基准电压源、大幅节省成本和PCB面积的方式解决了这个问题。每个调节器都有一个独立的使能引脚。当使能输入的电压升至 VIH_EN(最小值为0.9 V)以上时,器件退出关断模式,且管理模块开启,但不会激活调节器。将使能输入的电压与一个精密内部基准电压(典型值为0.97 V)相比较。一旦使能引脚的电压升至高于精密使能阈值,则调节器被激活,输出电压开始升高。 在输入电压和温度转折处,基准电压的变化幅度只有±3%。这一小范围变化可确保精密的时序控制,解决采用分立器件时遇到的各种问题。

当使能输入的电压降至低于基准电压低80 mV(典型值)时,调节器停用。当所有使能输入上的电压都降至VIL_EN(最大值 为0.35 V)以下时,器件进入关断模式。在该模式下,功耗降至1 μA 以下。图3 和图4 展示了用于Buck1 的ADP5134 精密使能阈值在温度范围内的精度。

图3. 温度范围内的精密使能导通阈值(10 个采样)

图4. 温度范围内的精密使能关闭阈值(10 个采样)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)