. 总结针对计算应用的典型同步降压调节器负载设计规范;Tjcn、负载电流、DC和瞬态调节

. 简单概述带来典型的每相20 - 30 A电流的因素;工作频率、瞬态响应和效率

. 解释三要素概念=>额定输出电流由三个因素确定:输出功率/电流、效率,以及Tjcn-amb热阻抗

. 总结功率级(Power Stage)器件设计特性,优化效率和热阻抗

. 展示在效率、功率损耗和温升等方面的测量数据

. 解释采用如何测量安装在电源板上的零部件的热阻抗

. 探讨受输出电压影响的效率和热阻抗,及所产生的HS/LS占空比(duty cycle)

. 结论

II.典型的同步降压计算负载规范针对典型的同步降压调节器计算负载需求,对功率级系列部件进行优化。这些应用将具有大范围的电流水平且可以是单相或者多相。通过在每相基准上比较电源系统(power train)规范,我们注意到,许多设计显示了共同的工作范围。典型的每相电源系统规范为:

. 电源系统占空比为5 % - 40 %

. 工作频率:300 kHz到600 kHz

. 负载功率:25 W

. 负载电流:25 A

针对此设计范围,已对部件的功率级设定进行了优化。选择了最通用的设计作为目标工作点- 12 Vin, 1 V / 25 A 输出。

III.决定负载规范的因素上述的参考设计规范—占空比、频率、功率和电流—是通过平衡相当广泛的电气和散热限制来设定的。对于典型的多相CPU电源,这些限制包括:

. 静态负载运行期间的输出峰峰值电压纹波

. 负载瞬变期间的输出电压偏移

. 系统温升极限

. 硅Tjcn设计极限

. 输入电流纹波

将会讨论每个设计因素的影响,以及折衷方案如何推动电源系统规范达到每相电流极限和工作频率。

满足这些系统性能目标需要平衡相互冲突的要求。对于稳态和瞬态负载,设计必须具有低输出电压纹波。每相DC电流、峰峰值纹波电流和工作频率都会影响输出调节。通过增加电源系统电感,可以减少静态输入和输出纹波,但较大的电感将会降低供电瞬态性能。较高的工作频率将减少纹波并改进瞬态性能,但较高的工作频率将会引起效率降低,因为增加了开关损耗,由此增加了器件的温升。

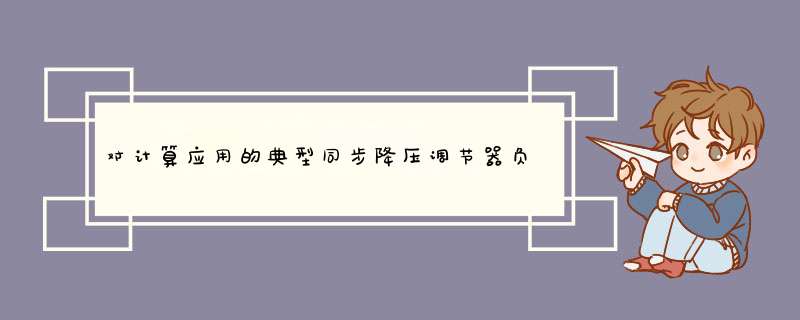

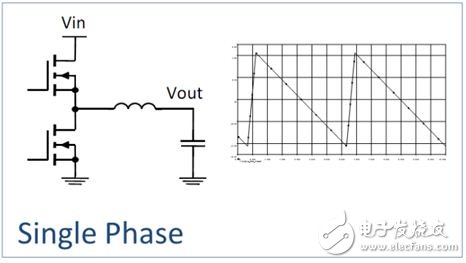

用于解决此局限的设计方法就是将总负载电流分成几个并联的电源系统,且允许每个都有相对高的纹波电流值。图1和图2显示了单相设计与多相设计的纹波电流比较。

图1. 单相纹波电流

图2. 多相纹波电流

多相设计的优势为几个低频单相电源系统的电流交错。这带来了较低的峰峰值纹波和较高的纹波频率。对于给定的纹波电压,还允许减少输出电容数。对于每一个电源系统,可以使用小电感来实现良好的瞬态响应。但这将导致纹波的增加。通过相电流的交错,将减少产生的输出电流纹波,同时仍然允许良好的瞬态响应。另外,大多数控制器具有瞬态运行模式,允许对准各个相位,用于优化转换速率。

对于给定的电感/电容元件的设置,较高的工作频率将导致纹波减少并改进瞬态响应;或者设计人员可以选择保持纹波恒定,并减少电感和输出电容元件的尺寸。

注意,通过增加电源频率或减少输出电感,无法单独满足CPU负载的初始急速瞬态阶段要求。需要低阻抗陶瓷电容的网格运作来满足初始瞬态。但在减少剩余的输出电容方面,更快的电源瞬态响应是有效的。

典型的每相25A、300kHz – 600kHz电源系统规格,是基于这些限制条件的最佳平衡。因此针对这一电流和频率范围所设计的器件将涵盖范围广泛的应用。

IV.三要素当新的部件发布时,我们常常会询问它的额定电流。飞兆半导体的数据表使用行业标准方法来规定额定电流,基于元件放置在极大的散热器上,并测量每个芯片发热达到其额定Tjcn额定值时所需要的电流。这使得可替换元件之间容易比较,但在实际电源应用中对部件的有效电流能力的理解有些局限。

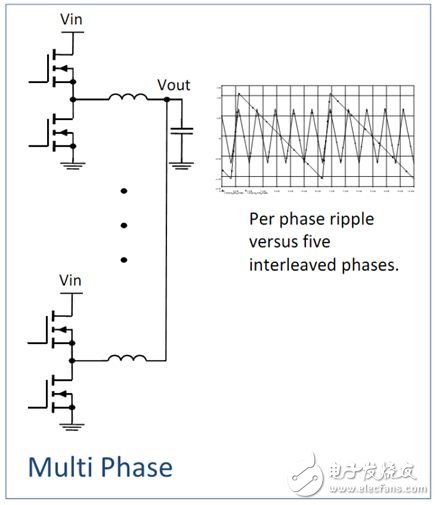

就像一只三条腿的凳子,部件的有效额定电流将基于三个不同因素的平衡:

. 输出功率

. 效率

. Jcn-Ambient 热阻抗

如图3所示,对于在期望的额定电流上运行的部件,它必须满足这三个限制因素的平衡;功率(Vout x Iout)、效率和热阻抗。图3中,25 A的灰色平面与曲面相交部分显示了在Vout = 1 V时,实现25 A所需的效率和阻抗组合。例如,假如设计的效率为90%,那么它必须具有低于14 C / W的热阻抗,以便保持温升低于40 C。

图3. 额定电流与效率和热阻抗的比较

由于在过去的五年里器件性能得到了改进, 25 A输出设计已经从一个三或四个FET D-PAK设计演变为一个双FET结构,并且现在已经演变为单一的5 mm x 6 mm功率级双芯片。图4显示了在电源系统尺寸方面的显著减少,这些已在这段时间内发生。

图4. 对于25 A设计的电源系统演变

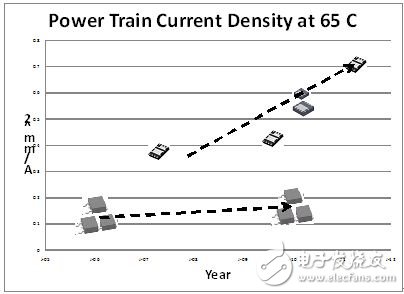

可以使用A/mm^2来表述此尺寸方面的改进,这里mm^2尺寸是安装部件所需的线路板面积尺寸。这包括封装外形加上焊接位占位面积。图5显示了在密度方面的演变,它们是从一系列飞兆评测板上观测到的,而这些评测板在过去五年里一直进行测试。

图5. 电源系统电流密度

在以下章节中,将回顾飞兆半导体能够实现功率密度的显著提高的设计改进。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)