FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

这篇文章主要就是谈论基于FPGA的UART模块的设计,一起来了解一下详细的信息。

在计算机的数据通信中,外设一般不能与计算机直接相连,它们之间的信息交换主要存在以下问题:

(1)速度不匹配。外设的工作速度和计算机的工作速度不一样,而且外设之间的工作速度差异也比较大。

(2)数据格式不匹配。不同的外设在进行信息存储和处理时的数据格式可能不同,例如最基本的数据格式可分为并行数据和串行数据。

(3)信息类型不匹配。不同的外设可能采用不同类型的型号,有些是模拟信号,有些是数字信号,因此采用的处理方式也不同。

为了解决外设和计算机之间的信息交换问题,即需要设计一个信息交换的中间环节——接口。UART控制器是最常用的接口。

通用异步收发器(Universal Asynchronotls Receiv—er/Transmitter,UART)是辅助计算机与串行设备之间的通信,作为RS 232通信接口的一个重要的部分,目前大部分的处理器都集成了UART。

一、UART的数据格式

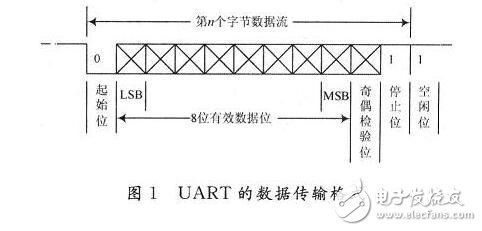

UART的数据传输格式如图1所示。

由于数字图像亚像素在计算机中是用8位二进制表示,因此UART传输的有效数据位为8位。传输线在空闲时为高电平,因此有效数据流的开始位设为0。接着传输8位有效数据位,先从最低位开始传送。

奇偶检验位可以设置为奇检验、偶校验或者不设置校验位,由于本系统使用的传输速率不高,为了加快开发进程,减少电路面积,因此没有设计奇偶检验模块,数据流中不设奇偶检验位。最后停止位为高电平。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)