一、 引言

MOSFET作为主要的开关功率器件之一,被大量应用于模块电源。了解MOSFET的损耗组成并对其分析,有利于优化MOSFET损耗,提高模块电源的功率;但是一味的减少MOSFET的损耗及其他方面的损耗,反而会引起更严重的EMI问题,导致整个系统不能稳定工作。所以需要在减少MOSFET的损耗的同时需要兼顾模块电源的EMI性能。

二、 开关管MOSFET的功耗分析

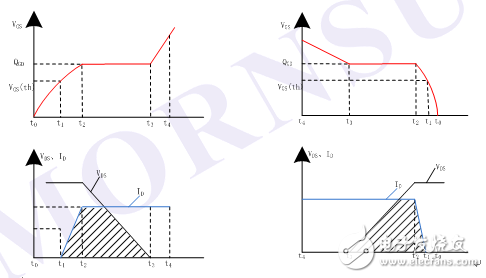

图1.MOSFET截止-导通波形转换 图2.MOSFET导通-截止波形转换

MOSFET的损耗主要有以下部分组成:1.通态损耗;2.导通损耗;3.关断损耗;4.驱动损耗;5.吸收损耗;随着模块电源的体积减小,需要将开关频率进一步提高,进而导致开通损耗和关断损耗的增加,例如300kHz的驱动频率下,开通损耗和关断损耗的比例已经是总损耗主要部分了。

MOSFET导通与关断过程中都会产生损耗,在这两个转换过程中,漏极电压与漏极电流、栅源电压与电荷之间的关系如图1和图2所示,现以导通转换过程为例进行分析:

t0-t1区间:栅极电压从0上升到门限电压Uth,开关管为导通,无漏极电流通过这一区间不产生损耗;

t1-t2区间:栅极电压达到Vth,漏极电流ID开始增加,到t2时刻达到最大值,但是漏源电压保持截止时高电平不变,从图1可以看出,此部分有VDS与ID有重叠,MOSFET功耗增大;

t2-t3区间:从t2时刻开始,漏源电压VDS开始下降,引起密勒电容效应,使得栅极电压不能上升而出现平台,t2-t3时刻电荷量等于Qgd,t3时刻开始漏极电压下降到最小值;此部分有VDS与ID有重叠,MOSFET功耗增大

t3-t4区间:栅极电压从平台上升至最后的驱动电压(模块电源一般设定为12V),上升的栅压使导通电阻进一步减少,MOSFET进入完全导通状态;此时损耗转化为导通损耗。

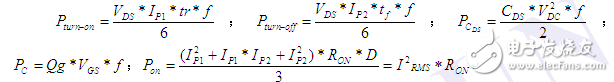

关断过程与导通过程相似,只不过是波形相反而已;关于MOSFET的导通损耗与关断损耗的分析过程,有很多文献可以参考,这里直接引用《张兴柱之MOSFET分析》的总结公式如下:

备注: 为上升时间, 为开关频率, 为下降时间, 为栅极电荷, 为栅极驱动电压 为MOSFET体二极管损耗。

三、 MOSFET的损耗优化方法及其利弊关系

3-1. 通过降低模块电源的驱动频率减少MOSFET的损耗

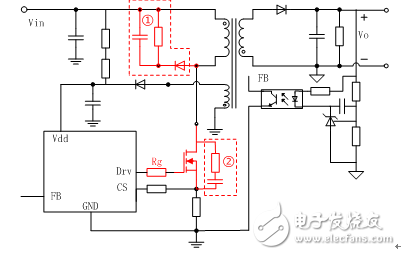

图3.反激开关电源一般框图

3-2.通过降低 、 来减少MOSFET的损耗

典型的小功率模块电源(小于50W)大多采用的电路拓扑结构为反激形式,典型的控制电路如图3所示;从MOSFET的损耗分析还可以知道: 与开通损耗成正比、 与关断损耗成正比;所以可以通过减少 、 来减少MOSFET的损耗,通常情况下,可以减小MOSFET的驱动电阻Rg来减少 、 时间,但是此优化方法却带来严重的EMI问题;以金升阳URB2405YMD-6WR3产品为例来说明此项问题:

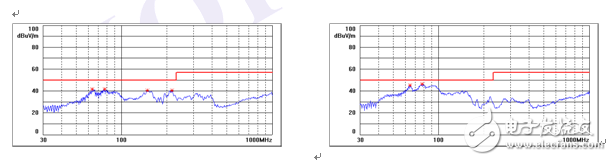

1) URB2405YMD-6WR3采用10Ω的MOSFET驱动电阻,裸机辐射测试结果如下:

图4 辐射骚扰水平极化方向测试结果 图5 辐射骚扰垂直极化方向测试结果

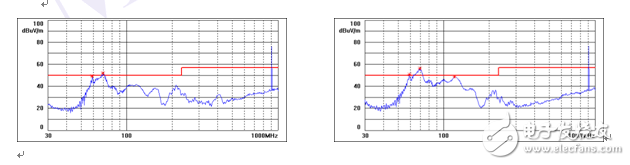

2) URB2405YMD-6WR3采用0Ω的驱动电阻,裸机辐射测试结果如下:

图6 辐射骚扰水平极化方向测试结果 图7 辐射骚扰垂直极化方向测试结果

从两种不同的驱动电阻测试结果来看,虽然都能够通过EN55022的辐射骚扰度的CLASS A等级,但是采用0欧姆的驱动电阻,在水平极化方向测试结果的余量是不足3dB的,该方案设计不能被通过。

3-3.通过降低吸收电路损耗来减少损耗

在模块电源的设计过程中,变压器的漏感总是存在的,采用反激拓扑式结构,往往在MOSFET截止过程中,MOSFET的漏极往往存在着很大的电压尖峰,一般情况下,MOSFET的电压设计余量是足够承受的,为了提高整体的电源效率,一些电源厂家是没有增加吸收电路(吸收电路如图3标注①RCD吸收电路和②RC吸收电路)来吸收尖峰电压的。但是,不注意这些吸收电路的设计往往也是导致EMI设计不合格的主要原因。以金升阳URF2405P-6WR3的吸收电路(采用如图3中的②RC吸收电路)为例:

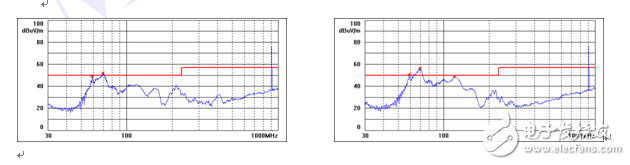

1) 驱动电阻Rg为27Ω,无RC吸收电路,辐射骚扰度测试结果如下:

图8 辐射骚扰水平极化方向测试结果 图9 辐射骚扰垂直极化方向测试结果

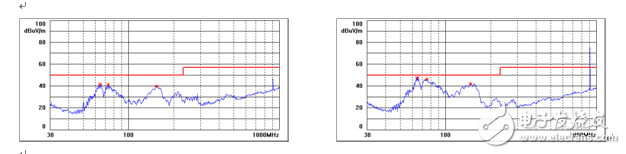

2)驱动电阻为27Ω;吸收电路为电阻R和C 5.1Ω 470pF,辐射骚扰度测试结果如下:

图10 辐射骚扰水平极化方向测试结果 图11 辐射骚扰垂直极化方向测试结果

从两种不同的吸收电路方案测试结果来看,不采用吸收电路的方案,是不能通过EN55022辐射骚扰度的CLASS A等级,而采用吸收电路,则可以解决辐射骚扰度实验不通过的问题,通过不同的RC组合方式可进一步降低辐射骚扰。

四、总结

MOSFET的功耗优化工作实际上是一个系统工程,部分优化方案甚至会影响EMI的特性变化。上述案例中,金升阳R3系列产品将节能环保的理念深入到电源的开发过程中,很好地平衡了电源整体效率与EMI特性,从而进一步优化了电源参数。将电源参数进一步优化,更能兼容客户系统,并发挥真正的电子系统“心脏”作用,源源不断的输送能量。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)