芯片制造商在前沿面临越来越多的挑战和权衡,其中工艺微缩的成本已经过高并且还在上升。虽然理论上可以将数字逻辑扩展到 10 埃 (1nm) 及以下,但在这些节点上开发平面 SoC 的可能性似乎越来越小。

在过去几十年里一直听到有关摩尔定律消亡的预测的行业中,这并不令人震惊。然而,令人惊讶的是,经过市场验证的替代品数量令人眼花缭乱,而且还在不断增长。该列表中包括各种类型的高级封装,其中一些已经在使用中,以及大量新材料、新颖的互连方案以及增加现有工艺节点密度的不同方法。因此,即使几乎所有的设计或制造障碍都可以通过足够的时间、努力和投资来克服,但在大多数情况下,有多种方法可以通过提高性能、降低功耗以及在某些情况下以更低的功耗来实现相同的目标成本。

“我们最近看到的趋势是,能够将最先进规模技术的价值货币化的公司越来越少,” Lam Research计算产品副总裁 David Fried 说。 “5nm 的客户比 7nm 的客户少,7nm 的客户比 10nm 的客户少,因为能够从开发这些新产品所需的大量资本投资中获取价值的公司数量较少。你会看到这种趋势继续下去。如果你不能在财务上利用微缩的价值,无论是功率、性能、面积还是产量,那么你不应该扩展。这个决定必须在产品层面做出。某些产品将由其所有者分析固定成本和经常性成本,所有者将决定如果您停留在 7 纳米而不跳到 5 纳米,业务方面会更好地工作。你会看到很多公司都会做出这样的决定。”

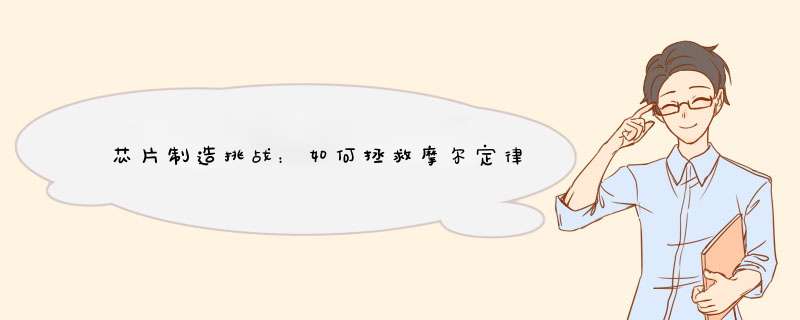

图 1:摩尔定律及其实际应用。资料来源:Max Roser,Hannah Ritchie,CC BY 4.0 ,来自Wikimedia Commons/Wikipedia 虽然一些设备和市场将支持扩展的持续经济性,但目前尚不清楚在单个 SoC 中与高级封装相比将完成多少。 “公司对他们想要使用最先进技术制造的产品非常挑剔,”Fried说。“他们正在使用最先进的技术制造产品中以密度为中心的部分,这完全是一种功能集成。即使他们没有通过访问那些高级节点来获得直线数据流性能,他们也会在相同的足迹中获得更多的数据流和数据路径。很明显,他们进行了计算,表明他们可以在产品层面获利是一个优势。”

但是,每个自定义配置都有其独特的权衡。对于平面缩放,这些权衡是有限的,因为它们是由制造工艺规则定义的。展望未来,需要在如何封装和使用芯片的背景下考虑权衡。因此,一个设备可能包括在不同工艺节点上开发的不同芯片或小芯片,这些可能会因最终应用和用例以及正在处理的数据类型而有很大差异。在 AI/ML 的情况下,它可能会因所需的准确度或精度水平而异。

更糟糕的是,还需要根据可变性以及封装或系统中其他组件的上下文来理解设备。噪声会影响相邻芯片中的信号完整性。机械应力会导致翘曲并影响各种类型的互连。清洁、抛光、剥离和蚀刻留下的纳米级颗粒会破坏系统的功能。组件的可用性、EDA 工具的差距和人才短缺也是如此。 随着选项数量的增加以及芯片制造商针对不同终端市场客户的需求,选择变得更加混乱。例如,在汽车领域,有多种可能的架构来处理安全关键数据,不同的汽车制造商通常采用独特的方法来优化各种功能。同样,云数据中心已经开发并继续完善针对其特定需求和数据类型而设计的芯片架构。在其他市场中,软件功能越来越多地与专门为这些功能开发的硬件相匹配,无论这些功能是集成到单个芯片中,还是因为超过标线限制而被拼接在一起的多个芯片,或者是在一个封装内集成多个不同的芯片或小芯片。

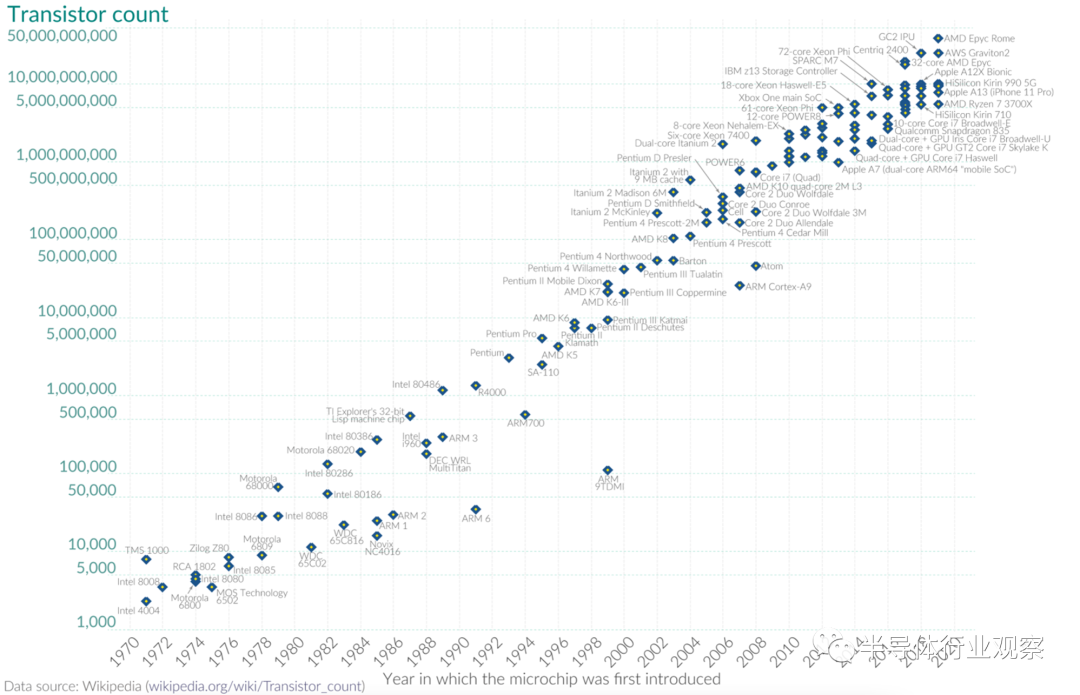

“某些技术对某些解决方案或某些问题有好处,但它们不会对所有事情都有好处,”imec 高级研究员 Eric Beyne 说。“因此对于扇入和扇出以及层压系统级封装,确实有一整套有用的技术。但这取决于您要解决的问题。如果您考虑手机中的 RF 模块,它们实际上是一个封装中 50 个组件的集合。但这些是连接相对较少的组件。你不能为 AI 内存逻辑分区做同样的互连密度。”

图 2:3D 互连预测。 资料来源:imec 在这种情况下,缩放只是前沿设计中的众多因素之一,甚至同一封装内的数字逻辑也可能在不同节点上开发,这取决于各种类型的数据对最终用户的重要性。例如,越来越多地包含在设备中的 AI 处理(或机器学习或深度学习)数据使用与 CPU 或 MCU 中的传统处理元素截然不同的架构。 AI芯片中结果的准确性和及时性取决于数据在本地存储器之间来回移动的速度、不同处理元素的性能和数据量——质量越多越好——以及这些芯片是否被用于数据中心或边缘设备。它可能需要进一步改进以启用并行或异步处理,或两者兼而有之。但是,虽然这对 AI 芯片很有效,但对于设备内其他类型的数据或功能来说,它绝对不是一种节能方法。

更多前进的方法

虽然一度被视为半导体进步的基准,摩尔定律本身正在分裂。技术缩放可但以继续,但平面缩放的经济性变得难以证明是合理的。在 3nm 工艺上获得足够的良率将是一项挑战,仅仅能够在越来越密集的晶体管海洋中提供电力可能需要背面供电,这反过来将改变晶圆厂和芯片在晶圆厂中的处理方式。 尽管如此,仍然没有单一的技术阻碍持续扩展。JCET首席技术官 Choon Lee 表示:“易碎的低 k 介电层一直是较新节点的一个问题。“但即使到 5nm 也没有重大工艺问题。虽然晶圆锯切可能是一项关键工艺,但如今激光开槽工艺和参数已明确定义。”

真正的限制因素是成本,这促使芯片制造商寻找替代方案,例如在高级封装中混合多个小芯片,并从每个节点中获得更多收益。这为过去讨论过的技术打开了大门,但当扩展被认为是最好的前进道路时,这些技术从未被广泛采用。 使用多束电子束光刻在掩模上打印曲线形状的能力就是这样一种技术。与打印畸形多边形或方孔相比,可以打印的设备形状要准确得多。这反过来又允许在现有节点上实现更大的密度。

“有了 EUV 光刻,事情变得容易多了,” D2S首席执行官 Aki Fujimura 说。“使用 EUV 比使用 193i 更容易打印出要求您打印的形状。所有领先的晶圆厂都处于“2nm节点”开发的研发阶段。ASML 的路线图有下一代 EUV 技术,称为“High NA”,使用 0.55 的数值孔径而不是今天的 0.33 来提高分辨率。但即使使用 EUV,超过 2nm 也将是一个挑战。只是没有足够的光子,而且存在随机效应。在这些方面,它真的开始变得重要了。”

实际上,这是缩小各种组件(例如晶体管和存储器)之间“white space”的一种方式,因为可以更准确地打印形状并使其更紧密地结合在一起。 “即使我们有一个纯粹的‘曼哈顿’设计——所以布局设计师从头到尾绘制这两个矩形,无论最小设计规则是什么,即使在晶圆上使用精细的OPC来控制光刻线和回拉”,Siemens EDA产品开发高级总监 John Sturtevant 说:“新的是,有了这些多光束掩模写入器,我们可以更积极地进行 OPC 校正。而且我们可以利用这样一个事实,如果我们知道我们将有一个弯曲的线性掩模,我们可以变得非常激进,并以一种掩模作者会因为没有足够的成本效益权衡而受到惩罚的方式利用这种曲率。” 最重要的是,缩放开始走向垂直,因此不再以平方毫米为单位测量芯片,而是越来越多地以立方毫米为单位进行测量。这增加了整个供应链的全新复杂性,从设计工具到机械应力和各种粘合技术。这也使得检查和测量从材料沉积和蚀刻到新材料的所有内容变得更具挑战性,并解释过去从未被视为问题的运动。

Brewer Science首席开发官 Kim Arnold 表示:“我们在quasi-zero die转移方面有一个非常活跃的计划。。 “您希望能够放置die并让它们在成型后移动不到一微米。对于芯片来说,这是他们从die-attach film获得的根本区别。因此,如果您放置一些die-attach film,它们可能会移动很多。我们已经展示了post-mold移动的结果小于一微米。您放下材料,放置芯片,构建 RDL 结构,然后进行成型。模前你看不出有什么不同,但模后你会看到。那是环氧树脂模塑料进入顶部,增加了压力并移动了东西。但是,该行业准备好替代环氧模塑料了吗?到目前为止,我们听到的答案是“不”。他们对 EMC 发生的事情并不满意,但谈论替代品还不够痛苦。”

与芯片行业的大部分历史一样,扩展已被充分理解和证明的东西总是比转移到未经尝试的东西更容易。这发生在光刻、晶体管结构、材料、各种制造工艺以及 EDA 工具上。这反过来又会影响添加和采用新方法的速度。业内人士仍然提到过去的转变,例如在 130nm 节点从铝互连转换为铜互连,或者在 16/14nm 节点从平面晶体管转换为 finFET。随着可靠性问题的增加,这些类型的移动尤其困难,而且它们更加耗时和昂贵。 “芯片最后,RDL 优先,只有在芯片第一次用尽时才会出现,”Arnold说。“因此,如果quasi-zero die 移位之类的东西在工艺流程中被证明是成功的,它将延迟chip last,因为这些工艺是已知的。因此,如果他们能够在 RDL 中达到他们的目标尺寸,那么chip first将尽可能地走得更远。在那之后,您将看到chip last的出现。chip last仅适用于那些需要严格 RDL 和高密度并且它们不能容忍任何变化的应用。

垂直扩展也带来了需要解决的热挑战。即使在平面裸片上使用finFET和环栅 FET(纳米片、纳米线等)也是如此,在这种情况下,动态功率密度可能会变得非常成问题,以至于任何时候都只能使用一些晶体管。但随着芯片堆叠在一起,这些问题更具挑战性。

Amkor全球测试服务高级主管 Warren Wartell 说:“有很多隐藏的影响,所以即使你有一个‘经过验证的芯片’,你也从来没有在这个封装中测试过它。”。 “你可能有局部加热,那个包装上有不同的压力梯度,这导致变化的方式与你预期的不同。因此,您需要拥有“有资格进行异构集成”的裸片,而这些裸片将成为您制造这些片上系统或系统级封装类型设备的标准构建块。您需要在上下文中进行测试,并进行足够的测试,以便您真正探索处理器的角落。这不是关于,‘我们有很多,一切都很好。当你遇到问题并且你质疑它为什么会失败时。也许是因为你从来没有真正探索过你的流程角落,以至于知道你在那里有一些敏感性。这些可能更难模拟,而且在进入大批量生产之前需要做更多的工作。”

小芯片之路

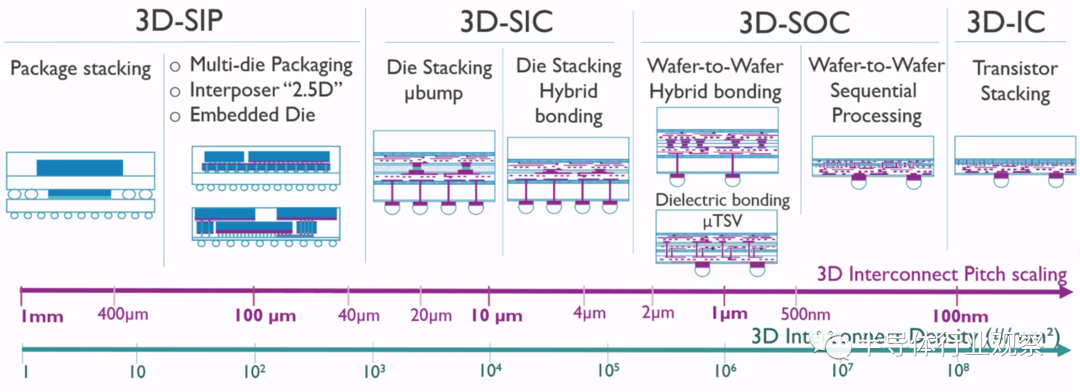

有多种封装类型可供选择。过去,封装仅能保护电子电路免受损坏。但封装技术本身正在变得更加定制化。 ASE营销和传播总监 Evelyn Lu在最近的一篇博客中指出了系统级封装的各种应用即使在几年前,也会在 PCB 上的一个或多个芯片上完成。但是,在可听设备(助听器、蓝牙耳塞、智能手表和智能眼镜)等应用中,对更小尺寸的需求需要将多个芯片集成在一个非常小的封装中,并且功耗非常低。她写道:“例如,可以将 30 多个组件集成到 4 毫米 x 8 毫米或 4.55 毫米 x 9 毫米大小的单个芯片上,从而将产品尺寸和整体重量大大减少 1 克或更多。”

图 3:助听器 SiP 和模块。 资料来源:ASE 可以使用目前正在开发的行业标准来表征和连接小芯片,从而进一步加快这一进程。目标是增加设计的灵活性,缩短上市时间,并显着减少开发电子系统所需的 NRE。 “在我职业生涯的前 20 年,我们主要进行单片 SoC 集成,”台积电业务发展高级副总裁 Kevin Zhang 说。“你可以将所有功能整合到一个芯片中——CPU、GPU、内存控制器。但现在人们意识到已经达到了极限。所以你把它分成几块,我们称之为小芯片。有时您可以选择针对特定功能优化的不同技术选项。这只是开始。这一切都始于 HPC,因为这是您目前获得最大收益的地方。但是未来我们会需要体积,而体积通常来自消费电子,无论是手机还是PC。这只是冰山一角,在未来,我们希望越来越多的产品——尤其是主流消费产品——能够从这种新的小芯片集成方案中受益,无论是成本、功耗还是外形尺寸,因为这些产品应用程序会转向这种方案。我们会提高音量,但我们还没有做到。”

提高小芯片体积的关键要素之一将是互连这些硬核 IP 块的可预测方式。为了实现这一目标,业界正在进行多项努力,其中一项来自开放计算项目的ODSA,另一项来自 Universal Chiplet Interconnect Express 小组。世界各地的政府机构也在制定自己的计划。

结论

未来的挑战将不是没有足够的选择来推进定制和半定制设计,或者摩尔定律正在失去动力。更大的障碍将是找出对于特定应用和终端市场而言,许多可能的选项中哪一个效果最好,或者至少足够好。 如果以以前的历史为指导,最终芯片行业将缩小可能性的数量,以实现规模经济并缩短上市时间。这是Makimoto 的 Wave的精髓,它在芯片行业的大部分历史中都是如此。但还有更多变数需要消化,更多变数即将出现,还有一堆以前从未存在过或从未如此严重依赖先进半导体技术的发展中市场。因此,芯片设计和制造重新转向商品化可能需要更长的时间。

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)