80C186XL16位嵌入式微处理器是Intel公司在嵌入式微处理器市场的上导产品之一。为了方便地使用DRAM,降低系统成本,本文提出一种新颖的解决方案:利用80C186XL的时序特征,采用CPLD技术,并使用VHDL语言设计实现DRAM控制器。

一、80C186XL RCU单元的资源

80C186XL的BIU单元提供20位地址总线,RCU单元也为刷新周期提供20位地址总线。80C186XL能够产生刷新功能,并将刷新状态编码到控制信号中。

嵌入式系统中DRAM控制器的CPLD解决方案

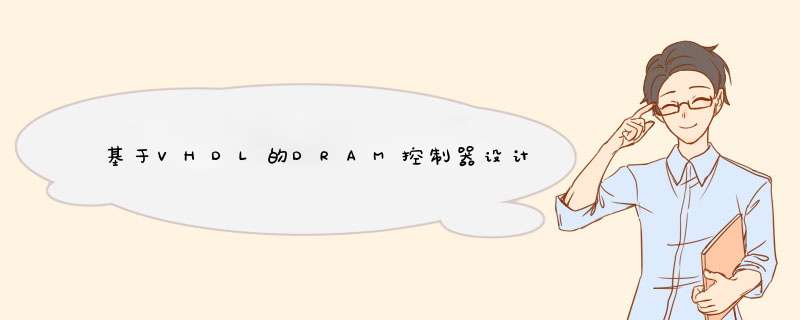

图1是RCU单元的方框图。它由1个9位递减定时计数器、1个9位地址计数器、3个控制寄存器和接口逻辑组成。当RCU使能时,递减定时计数器每一个CLKOUT周期减少1次,定时计数器的值减为1时,则产生刷新总线请求,递减定时计数器重载, *** 作继续。刷新总线周期具有高优先级,旦80C186XL总线有空,就执行刷新 *** 作。

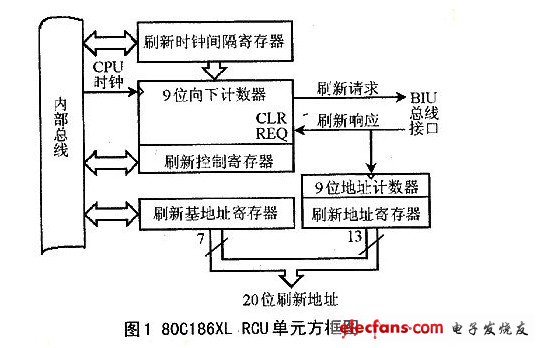

设计者可将刷新总线周期看成是“伪读”周期。刷新周期像普通读周期一样出现在80C186XL总线上,只是没有数据传输。从引脚BHE/RFSH和A0的状态可以判别刷新周期,如表1所列。刷新总线周期的时序要求如图2所示。

二、80C186XL DRAM控制器的设计与运行

DRAM存在着大量、复杂的时序要求,其中访问时间的选择、等待状态以及刷新方法是至关重要的。DRAM控制器必须正确响应80C186XL的所有总线周期,必须能将DRAM的部周期和其它访问周期分辨出来,其访问速度必须足够快,以避免不必要的等待周期。

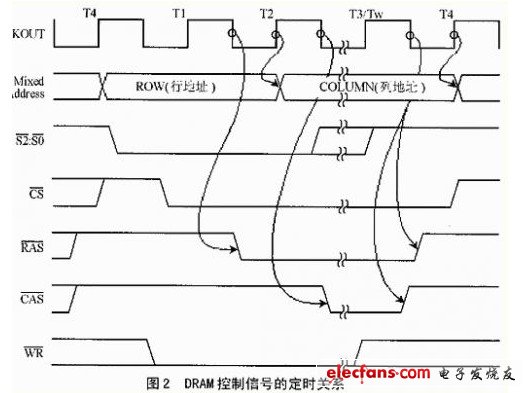

在设计时,我们采用XC95C36-15 CPLD[2]以及4Mbits的V53C8258[3]DRAM作范例。15ns的CPLD,速度相对较高,价格比较便宜。用它设计成的DRAM控制器允许80C186XL的工作速度高达20MHz,并且XC95C36有异步时钟选择项。这种特性对本设计有很大的好处。

图3是80C186XL DRAM控制器和存储器的功能框图。

DRAM控制器由80C186XL状态信号S2、S1和S0的解码来检测总线的开始、类型和结束。这些状态线是在CLKOUT的上升沿开始有效,在CLKOUT的下降沿失效的。DRAM控制器发出的RAS和CAS信号应该在CLKOUT的下降沿同时有效,行列地址应该在CLKOUT上升沿附近提供。

DRAM控制器应该在CLKOUT的两个沿都应能正常 *** 作。通过启用XC95C36的异步时钟选择项,每个XC95C36宏单元可以从可编程与阵列获得时钟。DRAM控制器使用80C186XL的CLKOUT信号作时钟输入。

DRAM控制器主要由两个相互联的状态机构成。这两个状态机,使得DRAM的控制与80C186XL是否进行等待状态无关。状态机A和地址多路控制信号(MUX)在CLKOUT的上升沿锁存。状态机B和RAS及CAS的逻辑在CLKOUT的下降沿锁存。DRAM控制器完整的VHDL语言的源代码可Email给cnhsx@sina.com索取。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)