文章将用VHDL设计八种常用的编码方式,并运用ALTERA公司的QUARTUSII设计软件进行仿真调试。QUARTUSII设计软件是一款开放、与结构无关、多平台、完全集成化、丰富的设计库、模块化工具、支持各种HDL、有多种高级编程语言接口的非常先进的EDA工具软件。另外,超高速硬件描述语言VHDL具有强大的语言结构、多层次的描述功能、良好的移植性和快速的ASIC转换能力,支持硬件的设计、综合、验证和测试。因此,应用VHDL设计通信编码波形具有重要意义。

总体方案设计

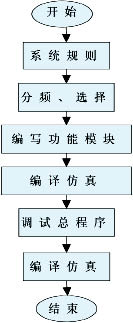

方案总体设计如图1所示。首先,在运用VHDL编写程序时必须遵照系统规则,按照系统库函数调用,否则编译将会产生问题。其次,考虑到分模块编程,而每一种编码方式的编程会用到不同频率的时钟,因此要将系统时钟二分频、四分频和八分频,以备需要。然后就是要设计选择模块,方便对八种编码的自由选择。再进行 各个编码模块的VHDL编码,进而可以逐个编译仿真。最后,当每一个模块编译仿真通过后,就是要将每一个独立模块程序整合在一起,形成总的编码程序,并且调试总程序。

图1 总体设计流程图

单元模块设计及调试

分频模块

工作原理

所谓分频,就是将一个给定频率较高的数字输入信号,经过适当的处理后,产生一个或数个频率较低的数字输出信号。分频本质上是加法器的变化,其计数值由分频常数N=fin/fout(fin是输入频率,fout是输出频率)决定,其输出不是一般计数器计数结果,而是根据分频常数对输出信号的高、低电平进行控制。

软件设计

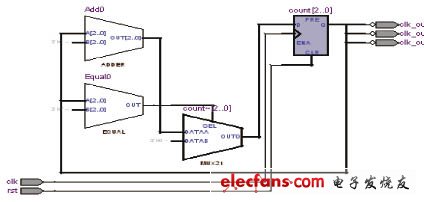

下面设计一个对输入时钟信号进行2分频、4分频和8分频的分频程序。根据实际需要还可以设计分频系数为2N的分频器,只需要实现一个模N的计数器,再把模N的计数器的最高位直接付给分频器的输出信号,即可得到所需要的分频信号。

分频系数是2的整数次幂的偶数分频器模块图如图2所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)