这里要明确两个概念:指令集规范(SpecificaTIon)和处理器实现(ImplementaTIon)是两个不同层次的概念,要区分开。指令集(ISA)是规范标准,往往用一本书或几张纸来记录描述,而处理器实现是基于指令集规范完成的源代码。RISC-V是一个指令集规范。

我们可以基于x86/ARM/ RISC-V指令集,进行处理器微架构设计和实现形成源代码,并通过流片最终形成芯片产品。其中指令集规范与处理器实现的知识产权是独立的,不能混为一谈。

"RISC-V是开源的"表示指令集规范是开源、开放和免费的(open and free),这与x86与ARM指令集有本质不同,但并不是指具体的处理器实现也都是开源免费的。

基于RISC-V指令集规范,既可以由开源社区来开发开源免费版的处理器实现(如Berkeley开发的Rocket核等),也可以有商业公司开发收费授权版的处理器实现(如国内平头哥玄铁910、芯来N200核与优矽渭河WH-32核等)。

(以上来源:https://mp.weixin.qq.com/s/9PX5n_ZPjWM1OyqnijlIPw,版权归文章作者所有)

国内厂商在做的工作RISC-V架构目前国内有不少院所和公司在做相关的工作,芯来,平头哥在做IP,兆易创新已经推出了基于芯来的N200定制的GD32VF103产品线,一些公司在基于平头哥的IP做SoC,嘉楠科技在去年推出了音视频AI专用的K210,中科蓝讯推出了一系列基于RISC-V架构的蓝牙芯片,出货量极大,其宣称是全球首家RISC-V应用量过亿(颗)的公司,而且全部搭载国产开源RT-Thread物联网 *** 作系统。公众号:OpenFPGA

(以上来源 链接:https://www.zhihu.com/quesTIon/274106611/answer/975894883,版权归作者所有)

更完整的总结查看《RISC-V指令集架构介绍及国内外厂商介绍》。

下面按照实现难度大致排序

新增1、TInyriscv tinyriscv完整的项目说明:

❝https://liangkangnan.gitee.io/2020/04/29/%E4%BB%8E%E9%9B%B6%E5%BC%80%E5%A7%8B%E5%86%99RISC-V%E5%A4%84%E7%90%86%E5%99%A8/

❞

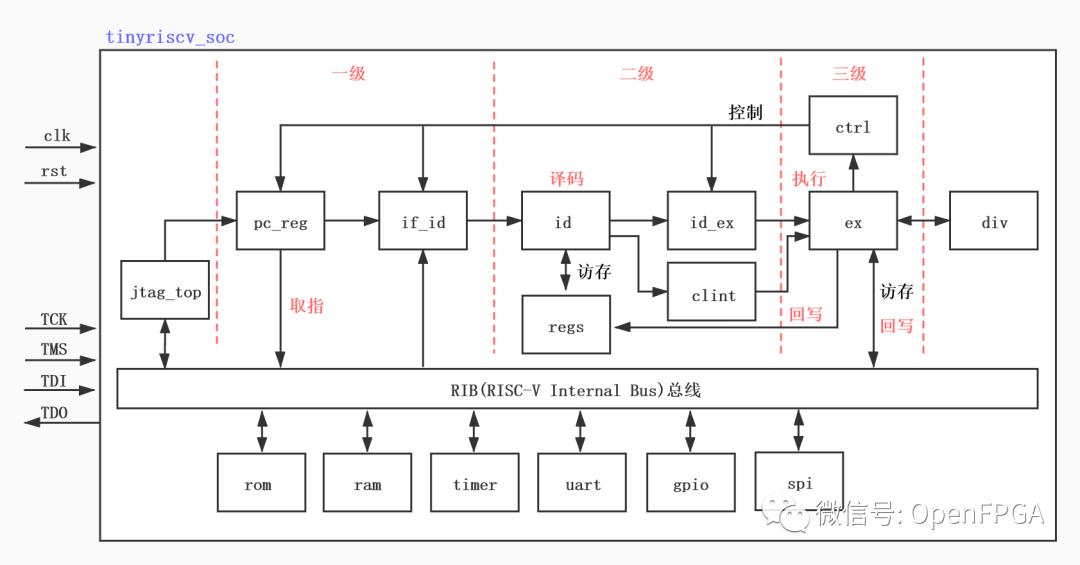

实现的是一个单核32位的小型RISC-V处理器核(tinyriscv),采用verilog语言编写。设计目标是对标ARM Cortex-M3系列处理器。tinyriscv有以下特点:

- 支持RV32IM指令集,通过RISC-V指令兼容性测试;

- 采用三级流水线,即取指,译码,执行;

- 可以运行C语言程序;

- 支持JTAG,可以通过openocd读写内存(在线更新程序);

- 支持中断;

- 支持总线;

- 支持FreeRTOS;

- 支持通过串口更新程序;

- 容易移植到任何FPGA平台(如果资源足够的话);

整体架构

❝https://gitee.com/liangkangnan/tinyriscv

❞

详细的中文设计说明,非常适合入门!

新增2、ridecore

❝https://github.com/ridecore/ridecore

RIDECORE (RISc-v Dynamic Execution CORE) 是一个用 Verilog HDL 编写的乱序 RISC-V 处理器。

RIDECORE 的微架构基于“现代处理器设计:超标量处理器的基础”(https://www.waveland.com/browse.php?t=624&r=d|259)。因此,我们建议用户在使用 RIDECORE 之前阅读本书和我们的文档 (doc/ridecore_document.pdf)。

到目前为止,我们的 FPGA 原型设计已经在 Xilinx VC707 板进行了原型验证。该原型可以在 50MHz 的时钟频率下运行。

ridecode的架构如下:

1、darkriscv

一晚从头开始实现开源RISC-V!

尽管与其他 RISC-V 实现相比,代码小而粗糙,但是作为初学或者初识RISC-V很友善(简易)。虽然很简易,但DarkRISCV具有许多令人印象深刻的功能:

- 实现大部分 RISC-V RV32E 指令集

- 实现大部分RISC-V RV32I指令集(缺少csr*、e和fence)

- 在超大规模 ku040 中工作频率高达 250MHz(400MHz 带超频!)

- 便宜的 spartan-6 高达 100MHz,适合小型 spartan-3E,例如 XC3S100E!

- 大多数时间(通常是 71% 的时间)可以维持每条指令 1 个时钟

- 灵活的哈佛架构(易于集成缓存控制器、总线桥等)

- 在 xilinx(spartan-3、spartan-6、spartan-7、artix-7、kintex-7 和 kintex ultrascale)中运行良好

- 与一些altera和lattice FPGA一起工作得很好

- 适用于 RISC-V 的 gcc 9.0.0(无需补丁!)

- 使用 850-1500LUT(核心仅使用 LUT6 技术,取决于启用的功能和优化)

- 可选的 RV32E 支持(与 LUT4 FPGA 配合使用效果更好)

- 可选的 16x16 位 MAC 指令(用于数字信号处理)

- 可选的粗粒度多线程 (MT)

- 流水线阶段之间没有互锁!

- BSD 许可证:可以在任何地方使用,没有限制!

是不是迫不及待去试一试了!

❝2、picoRiscVhttps://github.com/darklife/darkriscv

这个其实不需要过多介绍了,小巧且完善的RISC-V。

PicoRV32 是实现RISC-V RV32IMC 指令集的 CPU 内核。它可以配置为 RV32E、RV32I、RV32IC、RV32IM 或 RV32IMC 内核,并可选择包含内置中断控制器。

特点:

- 小型(7 系列 Xilinx 架构中的 750-2000 个 LUT)

- 高 fmax(7 系列 Xilinx FPGA 上为 250-450 MHz)

- 可选择的本机内存接口或 AXI4-Lite 主控

- 可选的 IRQ 支持(使用简单的自定义 ISA)

- 可选的协处理器接口

- 该 CPU 旨在用作 FPGA 设计和 ASIC 中的辅助处理器。由于其高fmax,它可以集成到大多数现有设计中,而无需跨越时钟域。当在较低频率下运行时,它会有很多时序裕量,因此可以添加到设计中而不会影响时序收敛。

❝官方地址:https://bitbucket.org/casl/shakti_public

❝3、cva6https://github.com/cliffordwolf/picorv32

CVA6 是一个 6 级、有序 CPU,它实现了 64 位 RISC-V 指令集。它完全实现了 I、M、A 和 C 扩展,如第 I 卷:用户级 ISA V 2.3 以及特权扩展草案 1.10 中所述。它实现了三个权限级别 M、S、U 以完全支持类 Unix *** 作系统。公众号:OpenFPGA

它具有可配置的大小、单独的 TLB、硬件 PTW 和分支预测(分支目标缓冲区和分支历史表)。主要设计目标是减少关键路径长度。

❝4、VexRiscvhttps://github.com/openhwgroup/cva6

用 SpinalHDL 编写的 RISC-V 实现。以下是一些规格:

- RV32I[M][A][F[D]][C] 指令集

- 流水线从 2 到 5+ 个阶段([Fetch*X]、Decode、Execute、[Memory]、[WriteBack])

- 1.44 DMIPS/Mhz --no-inline 当几乎所有功能都启用时(1.57 DMIPS/Mhz 当分频器查找表启用时)

- 针对 FPGA 进行了优化,不使用任何供应商特定的 IP /原语

- AXI4、Avalon、wishbone

- 可选的 MUL/DIV 扩展

- 可选 F32/F64 FPU(目前需要数据缓存)

- 可选的指令和数据缓存,

- 可选硬件重新填充 MMU

- 可选的调试扩展允许通过 GDB >> openOCD >> JTAG 连接进行 Eclipse 调试

- RISC-V 特权 ISA 规范 v1.10 中定义的机器、[Supervisor] 和 [User] 模式的可选中断和异常处理。

- 移位指令的两种实现:单周期(全桶式移位器)和shiftNumber周期

- 每个阶段可以有可选的旁路或互锁危险逻辑

- Linux 兼容(SoC:https : //github.com/enjoy-digital/linux-on-litex-vexriscv)

- Zephyr兼容

- FreeRTOS 端口

下面是运行的最高主频及消耗的资源:

VexRiscv small (RV32I, 0.52 DMIPS/Mhz, no datapath bypass, no interrupt) ->

Artix 7 -> 243 Mhz 504 LUT 505 FF

Cyclone V -> 174 Mhz 352 ALMs

Cyclone IV -> 179 Mhz 731 LUT 494 FF

iCE40 -> 92 Mhz 1130 LC

VexRiscv small (RV32I, 0.52 DMIPS/Mhz, no datapath bypass) ->

Artix 7 -> 240 Mhz 556 LUT 566 FF

Cyclone V -> 194 Mhz 394 ALMs

Cyclone IV -> 174 Mhz 831 LUT 555 FF

iCE40 -> 85 Mhz 1292 LC

VexRiscv small and productive (RV32I, 0.82 DMIPS/Mhz) ->

Artix 7 -> 232 Mhz 816 LUT 534 FF

Cyclone V -> 155 Mhz 492 ALMs

Cyclone IV -> 155 Mhz 1,111 LUT 530 FF

iCE40 -> 63 Mhz 1596 LC

VexRiscv small and productive with I$ (RV32I, 0.70 DMIPS/Mhz, 4KB-I$) ->

Artix 7 -> 220 Mhz 730 LUT 570 FF

Cyclone V -> 142 Mhz 501 ALMs

Cyclone IV -> 150 Mhz 1,139 LUT 536 FF

iCE40 -> 66 Mhz 1680 LC

VexRiscv full no cache (RV32IM, 1.21 DMIPS/Mhz 2.30 Coremark/Mhz, single cycle barrel shifter, debug module, catch exceptions, static branch) ->

Artix 7 -> 216 Mhz 1418 LUT 949 FF

Cyclone V -> 133 Mhz 933 ALMs

Cyclone IV -> 143 Mhz 2,076 LUT 972 FF

VexRiscv full (RV32IM, 1.21 DMIPS/Mhz 2.30 Coremark/Mhz with cache trashing, 4KB-I$,4KB-D$, single cycle barrel shifter, debug module, catch exceptions, static branch) ->

Artix 7 -> 199 Mhz 1840 LUT 1158 FF

Cyclone V -> 141 Mhz 1,166 ALMs

Cyclone IV -> 131 Mhz 2,407 LUT 1,067 FF

VexRiscv full max perf (HZ*IPC) -> (RV32IM, 1.38 DMIPS/Mhz 2.57 Coremark/Mhz, 8KB-I$,8KB-D$, single cycle barrel shifter, debug module, catch exceptions, dynamic branch prediction in the fetch stage, branch and shift operations done in the Execute stage) ->

Artix 7 -> 200 Mhz 1935 LUT 1216 FF

Cyclone V -> 130 Mhz 1,166 ALMs

Cyclone IV -> 126 Mhz 2,484 LUT 1,120 FF

VexRiscv full with MMU (RV32IM, 1.24 DMIPS/Mhz 2.35 Coremark/Mhz, with cache trashing, 4KB-I$, 4KB-D$, single cycle barrel shifter, debug module, catch exceptions, dynamic branch, MMU) ->

Artix 7 -> 151 Mhz 2021 LUT 1541 FF

Cyclone V -> 124 Mhz 1,368 ALMs

Cyclone IV -> 128 Mhz 2,826 LUT 1,474 FF

VexRiscv linux balanced (RV32IMA, 1.21 DMIPS/Mhz 2.27 Coremark/Mhz, with cache trashing, 4KB-I$, 4KB-D$, single cycle barrel shifter, catch exceptions, static branch, MMU, Supervisor, Compatible with mainstream linux) ->

Artix 7 -> 180 Mhz 2883 LUT 2130 FF

Cyclone V -> 131 Mhz 1,764 ALMs

Cyclone IV -> 121 Mhz 3,608 LUT 2,082 FF

VexRiscv有个官方的SoC:Briey,使用AXI接口。和Rocket Chip一样,支持Verilator+OpenOCD+GDB仿真。和Rocketchip一样都是使用scala解释器sbt工具.

关于Spinal,可以查看《从Verilog到SpinalHDL》。

❝https://github.com/SpinalHDL/VexRiscv

以上几个小项目都适合了解和入门RISC-V,简易是最大的特点,最主要的是都可以在FPGA开发板上运行,而且对FPGA要求也不高。

接下来就是几个成熟点的项目了。

5、平头哥无剑100平头哥无剑100

文档目录如下:

|--Project //open source project work directory

|--riscv_toolchain //tool chain install directory download from t-head.cn

|--wujian100_open //wujian100_open project get from github

|--case //test case example for simulation

|--doc //wujian100_open user guide

|--fpga //FPGA script

|--lib //compile script for simulation

|--regress //regression result

|--sdk //software design kit

|--soc //Soc RTL source code

|--tb //test bench

|--tools //simulation script and setup file

|--workdir //simulation directory

|--LICENSE

|--README.md

❝6、Hummingbirdv2 E203 Core and SoChttps://github.com/T-head-Semi/wujian100_open

芯来科技研发的一款RISC-V core&SOC,是SI-RISCV/e200_opensource (https://github.com/SI-RISCV/e200_opensource)的进阶版。

该存储库托管开源 Hummingbirdv2 E203 RISC-V 处理器内核和 SoC 的项目,它由基于中国大陆的领先 RISC-V IP 和解决方案公司Nuclei System Technology开发和开源。公众号:OpenFPGA

这是SI-RISCV/e200_opensource中维护的Hummingbird E203项目的升级版,所以我们称之为Hummingbirdv2 E203.

在这个新版本中,我们有以下更新。

- 为 E203 内核添加 NICE(Nuclei Instruction Co-unit Extension),因此用户可以轻松创建带有 E203 内核的定制硬件协同单元。

- 将PULP Platform的APB接口外设(GPIO、I2C、UART、SPI、PWM)集成到Hummingbirdv2 SoC中,这些外设采用Verilog语言实现,便于用户理解。

- 为 Hummingbirdv2 SoC 添加新的开发板(Nuclei ddr200t 和 mcu200t)支持。

欢迎访问https://github.com/riscv-mcu/hbird-sdk/使用蜂鸟 E203 软件开发包。

欢迎访问https://www.rvmcu.com/community.html参与蜂鸟E203的讨论。

❝https://github.com/SI-RISCV/e200_opensource

❝7、香山开源高性能处理器https://github.com/riscv-mcu/e203_hbirdv2

“香山”基于Chisel语言开发,支持多核,采用乱序执行、11级流水、6发射。采用28nm台积电工艺预计达到1.3Ghz主频,采用中芯国际14nm工艺预计达到2Ghz主频。性能评估为7/Ghz(SEPC2006),换言之,第一版的雁栖湖架构对标的是ARM A72/A73。

“香山”第二代南湖架构的目标是10/G,在采用中芯国际14nm工艺的情况下主频达到2Ghz。从参数上看,南湖架构对标的是A76,2G主频下SPEC06达到20分。如果能够实现这一设计目标,裸CPU性能在RISC-V处理器中是首屈一指的。

更详细介绍《不采用Verilog,RTL开源!国产香山RISC-V高性能处理器问世!乱序执行、11级流水、6发射!性能堪比A76》。

架构如下:

知乎首页:https://www.zhihu.com/people/openxiangshan

关于Chisel和Spinal介绍《https://zhuanlan.zhihu.com/p/89249985》。

❝8、木心处理器https://github.com/OpenXiangShan/XiangShan

木心处理器是一系列易于学习的 RISC-V 处理器和相关的基于 VSCode 的 IDE 称为 TreeCore,具有丰富、详细和交互式的在线教程,对初学者很友好。基于 VSCode 的 IDE 集成了代码分析、波形模拟功能,可以自动从云服务器中查找和组装特定的工具链、IP 核和库依赖项,以开发处理器或应用程序。

特征:

- 对verilog、vhdl、chisel 和spinalHDL 的完整语言支持。

- 现代用户界面

- 轻便、开箱即用的功能

- GPU 加速以实现快速实时渲染

❝9、Rockethttps://github.com/microdynamics-cpu/tree-core-ide

(UCB)标量处理器:64位、5级流水线、但发射顺序执行处理器,特征:

- 支持MMU,支持分页虚拟内存。可以移植到Linux *** 作系统

- 具有兼容的的IEEE 754-2008标准的FPU

- 具有分支预测功能,具有BPB(Branch Prediction Buff)、BHT(Branch History Table)、RAS(Return Address Stack)

Rocket同样采用Chisel语言编写;

❝10、BOOMhttps://github.com/freechipsproject/rocket-chip

(UCB)超标量乱序执行处理器;

-

BOOM也是采用Chisel编写,全部代码大约9000行;指令为RV64G

-

6级流水线:取指、译码/重命名/指令分配、发射/读寄存器、执行、内存访问、回写

❝11、Sodorhttps://github.com/riscv-boom/riscv-boom

(UCB)针对教学的32位开源处理器。Chisel编写,支持5种处理器:单周期处理器、2级流水线处理器、3级流水线处理器、5级流水线处理器、可执行微码的处理器。公众号:OpenFPGA

早期出于教学目的处理器,使用Chisel编写,没有什么实际商用价值。已经很长时间没有更新了。

结构相对清晰一些,如对不同深度PipeLine都有描述(分别有1阶、2阶、3阶和5阶);可以作为很好的示范代码

❝12、YARVIhttps://github.com/ucb-bar/riscv-sodor

VARVI是RISC-V爱好者Tommy Thorn设计发布的简单的、32位开源处理器,实现了RV32I,使用Verilog,目标是为了能够清晰准确的实现RV32I

❝13、Pulpinohttps://github.com/tommythorn/yarvi

由苏黎世联邦理工大学与意大利博洛尼亚大学联合开发。32位,指令集:RV32I/RV32C/RV32M,扩展了RISC-V指令;多核

❝网址:https://www.pulp-platform.org/

❝14、GRVI Phalanxhttps://github.com/pulp-platform/pulpino

大规模并行RISC-V(最多到千核),2~3级流水线,32位,其中在Artix-7 35T开发板上已经实现32 RISC-V处理器;在PYNQ-Z1上实现了80核;在UltraScale上实现了1680核的RISC-V;不开源

15、Ibex提到开源RISC-V就不能不提Riscy系列了,尤其是zero-riscy,使用很广泛。Ibex是脱胎于zero-riscy的core,支持RV32IMC及一些Z系列指令,由LowRISC维护。Ibex小巧精悍,文档详实,学习资料丰富,支持verilator, 可以使用verilator+openOCD+GDB 仿真时debug。对于我这样的重度Verilator依赖者来说非常友好。

Ibex支持machine mode和user mode两种privilege mode,可以实现比单machine mode更加丰富的功能。Ibex采用system verilog开发,对于传统的IC工程师是个好消息。Ibex现在也支持了指令cache了,提高了performance,但装了cache会让core变得臃肿很多,对于学习cache controller的设计是个好事情。

Ibex使用类TLUL的自定义接口,官方的SoC是PULP。Google的OpenTitan项目也是基于Ibex。相关的设计学习资料算是相当多了。

❝https://github.com/lowRISC/ibex

❝16、SweRV EH1文档:https://ibex-core.readthedocs.io/en/latest/introduction.html

SweRV EH1是WD开发的其中一款RISC-V core,支持RV32IMC,双发射,单线程,9级流水,性能应该说是相当不错,28nm可以跑到1GHz。而且还有份详细的文档,不愧是大厂出品。

SweRV是使用Verilog/System Verilog开发,使用AXI接口,对熟悉AMBA且不想去学Chisel及Scala的同学来说是相当友好了。而且支持verilator,必须点赞。值得一提的是SweRV带指令cache,且实现了丰富的cache maintenance自定义指令,非常值得学习。

❝https://github.com/chipsalliance/Cores-SweRV

大厂出品,进阶学习佳作。

17、picorio官方出品。

2017年图灵奖得主大卫·帕特森教授(David Patterson)领衔的RISC-V国际开源实验室(RIOS:RISC-V International Open Source Lab)发布了全球首个可运行Linux的全开源RISC-V微型电脑系统PicoRio项目,用于构建更透明、低功耗、定制能力强的高效能边缘计算平台。PicoRio最大的特点是从CPU设计,到PCB电路板设计,再到 *** 作系统核心软件全部开源,核心架构使用最新的开源RISC-V指令集技术。除高质量工业级的开源IP之外,PicoRio还将提供开源的参考SoC设计,以及详尽的集成文档。PicoRio基于开源的处理器,拥有许多IP的支持。在软件方面,PicoRio设计了一个整体软件架构,具有丰富的 *** 作系统环境以及其他程序的支持,因此拥有一个强大的软件生态。PicoRio的发布,标志着RIOS实验室进入了实际产出的阶段。之后,RIOS实验室将致力于在RISC-V生态下打造更开源、更低功耗和更安全的软硬件生态,并负责维护整个PicoRio的硬件系统和软件架构。

PicoRio项目涵扩了对Chromium OS内核以及V8 JavaScript 引擎的RISC-V平台移植和支持。可运行完整的Linux和FreeRTOS系统。PicoRio项目将于2021年完成ARM A75级别的芯片设计和验证,将用于 RISC-V 的平板电脑/笔记本电脑,其中所有应用程序软件和存储都在云中运行(类似 Chromebook)。

参考资料:

- PicoRio Specification:https://gitlab.com/picorio/picorio-doc

- RISC-V Specification: https://riscv.org/technical/specifications/

- RISC-V Tools https://github.com/riscv/riscv-tools

- RISC-V GNU Toolchain//github.com/riscv/riscv-gnu-toolchain

项目地址

❝审核编辑 :李倩https://rioslab.org

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)