1 前言

近年来,随着嵌入式核心芯片的飞速发展,改变了传统嵌入式系统的设计方法,嵌入式系统逐渐由板级向芯片级过渡,即片上系统——SOC。片上系统是追求产品系统最大包容的集成器件,是当前嵌入式应用领域的技术热点。SOC的出现使集成电路发展成为集成系统,整个电子整机的功能可以集成到一块芯片中,降低了设计成本,缩短了开发周期。因此,本文设计了一个基于FPGA的嵌入式系统,既能满足嵌入式系统教学实验的需要,同时也可作为嵌入式产品开发平台。

2 系统硬件设计

本系统要实现的功能包括:可以运行嵌入式 *** 作系统;支持NIOS II开发;支持USB通讯;支持RS-232串口通讯;支持以太网通讯;支持JTAG接口在线调试与下载。

2.1 系统硬件框图

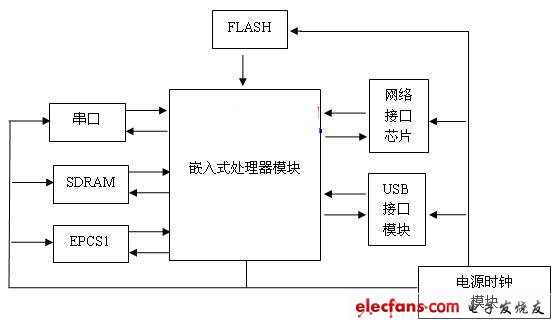

针对所需的功能,设计出系统的相应硬件平台,硬件平台主要是由嵌入式处理器模块、存储器模块、包括以太网接口、USB接口和电源等外部接口电路模块组成。系统硬件结构框图如图1 所示。

图1 系统硬件结构图

2.2 嵌入式处理器模块

2.3存储器模块

2.3.1 专用串行配置器件EPCS1接口电路

EPCS系列器件是Altera公司提供的一种基于FLASH存储器的专用串行配置器件,其具有串行接口,接口只需要四个引脚,能够存储StraTIx II 系列、Cyclone系列的FPGA的配置信息,并在系统上电或者需要重新配置FPGA时,向FPGA发送配置信息。本系统用的串行配置器件EPCS1大小为1M字节,反复擦写次数可多达十万,可以轻松实现掉电保护

2.3.2 Flash存储器接口电路

Flash存储器具有低功耗、大容量、擦写速度快、可整片或分扇区在系统编程(烧写)、擦除等特点,因而在各种嵌入式系统中得到了广泛的应用。

系统中用了一片AMD29LV320D FLASH存储器,其单片存储容量为32M位(4M字节),工作电压为2.7V~3.6V,16位数据宽度。AMD29LV320D仅需3V电压即可完成在系统的编程与擦除 *** 作,通过对其内部的命令寄存器写入标准的命令序列,可对Flash进行编程(烧写)、整片擦除、按扇区擦除以及其他 *** 作。

Flash存储器在系统中通常用于存放程序代码,系统上电或复位后从此获取指令并开始执行,由于,在进行系统整体设计时,可以通过使用Quartus II对引脚进行配置,所以对于AMD29LV320D FLASH的三个功能引脚nCE、nOE、nWE,可以各接一个EP1C12Q240C8的通用I/O脚即可。

2.3.3 SDRAM存储器接口电路

与Flash存储器相比较,SDRAM不具有掉电保持数据的特性,但其存取速度大大高于Flash存储器,且具有读/写的属性,因此,SDRAM在系统中主要用作程序的运行空间、数据及堆栈区。当系统启动时,CPU首先从复位地址0x0处读取启动代码,在完成系统的初始化后,程序代码调入SDRAM中运行,以提高系统的运行速度。同时,系统及用户堆栈、运行数据也都放在SDRAM中。

系统中用了一片HY57V641620 SDRAM存储器,其存储容量为4组x16位(8M字节),工作电压为3. 3V,常见封装为54脚TSOP,兼容LVTTL接口,支持自动刷新(Auto-Refresh)和自刷新(Self-Refresh), 16位数据宽度。可满足运行MicroC/OS *** 作系统、或者mClinux *** 作系统及各种相对较复杂的算法的运行要求。

要在系统中使用SDRAM,要求微处理器具有刷新控制逻辑,或在系统中另外加入刷新控制逻辑电路。通过Altera公司提供的NIOS II开发工具可以将SDRAM控制器添加到NIOS CPU中,然后下载到EP1C12Q240C8中运行,因此可以方便地使用EP1C12Q240C8的通用I/O口与SDRAM相连接,同样在进行系统整体设计时通过Quartus II定义引脚。

2.4 外部接口模块

2.4.1以太网接口设计

系统采用realteck公司推出多年RTL8019AS网络芯片。RTL8019AS芯片是一款应用广泛的10M网络芯片,支持以太网II 和IEEE802.3 10Base5,10Base2,10BaseT、支持可编程输出的4-诊断 LED。利用RTL8019AS可以在NIOS II系统中方便的建立起完整的网络服务器,可以通过网络从FPGA芯片构成的软嵌入式系统中收发数据。

RTL8019AS与EP1C12Q240C8通过外部总线进行连接。主要是把RTL8019AS的数据总线(SDO~SD15)、地址总线(SAO~SA5,SA8)、读使能(IORB)、写使能(IOWB)、中断输出信号(INTO)和中断输入信号(RSTDRV)与EP1C12Q240C8的通用I/O脚连接即可。

2.4.2 USB接口设计

系统采用Cypress公司的SL811HS芯片作为USB接口芯片,它是一种USB主机控制器,它能与全速或低速USB外围设备通信。SL811HS能与各种微处理器、微控制器、FPGA以及DSP,ISA等各种总线进行接口,适用于各种要求配置USB主机或设备的嵌入式系统。

在USB接口电路设计中,SL811HS的8位数据线直接和FPGA芯片的8位数据线相连。其中需要注意的是,SL811HS的AO引脚和低8位地址线的最低位AO相连,即与锁存器的地址输出端的最低位相连。

2.4.3 串行接口设计

RS232是应用最为广泛的UART接口,可以方便的实现与计算机的数据通讯;同时在调试基于FPGA的嵌入式 *** 作系统时候,可以作为辅助调试接口,结果输出到主机的超级终端上面。因为FPGA的通用I/O引脚可以在后期通过Quartus II软件定义,所以只需选取EP1C12Q240C8的任意四个引脚与电平转换器MAX3232C相连,通过MAX3232C 接RS232标准串行接口(DB9),可与PC机进行串行通信。

2.4.4 电源接口设计

系统需要使用1.5V、3.3V和5V三种直流电源,其中,EP1C12Q240C8内核使用1.5V电源,EP1C12Q240C8的I/O口、MAX3232C、LCD接口等器件使用3.3V电源,RTL8019AS使用5V电源。为简化系统电源电路的设计,要求整个系统的输入电压为高质量的5V直流电压电源,本系统采用电压转换芯片B1117来得到1.5V和3.3V的电压。

2.4.5 系统时钟电路设计

系统时钟模块为试验系统提供时钟信号,使其工作在指定的频率下,是系统不可缺少的部分。本系统的时钟信号由50MHz的有源晶振产生,为了使系统有稳定的时钟输入,要对晶振的输入电压通过简单的LC滤波电路做滤波处理,使其电压更加稳定,尽可能减小干扰。

2.4.6 复位电路设计

在系统中,复位电路主要完成系统的上电复位和系统在运行时用户的按键复位功能。本系统根据实际需要,通过Quartus II软件对复位信号进行延时设计,然后在外部再加以需要简单的电路来实现。

2.4.7 JTAG接口设计

JTAG(Joint Test AcTIon Group)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试 。JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路,可以通过专用的JTAG测试软件对芯片内部节点进行测试。EP1C12Q240C8有四个专用引脚TMS、TDI、TCK、TDO与Altera公司的专用下载电缆——Byte Blaster II通过一个十针的插座相连,用于下载以及在线调试。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)