电子发烧友网核心提示:获奖的Nios® II 嵌入式处理器C语言至硬件(C2H)加速编译器将对时间要求较高的ANSI C函数转换为FPGA中的硬件加速,从而提高了性能。

特性:

(1)ANSI/ISO C 代码按键式加速

(2)和软件设计流程的紧密集成

(3)硬件加速和 CPU 存储器映射的直接连接

(4)无缝支持指针和数组

(5)高效的存储器处理延迟预知调度和流水线

通过增加硬件来降低功耗

系统设计经验一直是认为增加硬件会提高功耗。但是,仔细的使用硬件加速打破了这一经验:增加硬件会降低功耗。通过分析算法,在可编程逻辑中实现合适的加速,您不但提升了嵌入式计算系统的设计性能,而且同时降低了功耗。

考虑这样一个实例,嵌入式设计人员希望处理器以80 MHz执行程序,将大计算量的算法卸载到时钟频率较低的硬件中。如表1所示,在实际测试中,嵌入式处理器以80 MHz运行应用程序代码,5个硬件加速以1 MHz运行,系统性能提高了6倍,同时系统功耗降低了55%。

大幅度提高嵌入式软件的性能

对于需要提高嵌入式应用软件性能的软件工程师而言,硬件加速是最重要的一种工具。硬件加速能够充分发挥FPGA并行处理结构的优势,与通用CPU相比,每个时钟周期完成更多的计算,性能提高了几个数量级。请参考表2,了解几种常用嵌入式算法的性能和面积结果。

表 1 注释:系统资源提高考虑了片内资源的逻辑单元等价成本,例如乘法器和存储器,显示了加入加速和缓冲之后增加的成本。这些数据表明, Nios II C2H 编译器能够以最小的成本和资源占用大大提升系统性能。

熟悉的软件设计流程

到目前为止,还一直由手动完成将软件卸载给硬件加速,只有那些拥有工具、经验和时间的开发人员才能利用这一技术建立、测试寄存器传送级 (RTL) 模块,并集成到处理器系统中。而 Nios II C2H 编译器自动建立并集成硬件加速,开发时间由几星期缩短到几分钟。

如果您以前曾经使用过基于 Eclipse 的 Nios II 集成开发环境 (IDE) ,那么采用 Nios II C2H 进行设计将非常简单。您所需要做的工作是:

分析软件代码,确定出现性能瓶颈的函数。

在 Nios II IDE 中高亮显示所需的函数,右键单击加速。

查看详细的 C2H 编译器报告文件,确定简单的 C 代码优化。

进行优化和迭代,直到达到所需的性能。

迅速达到您应用软件的性能要求,提前发售产品。

Nios II C2H 编译器使您能够快速高效的在设计空间中优化您的应用软件算法,仅针对软件实现来提升性能。您需要做的只是右键单击进行加速。

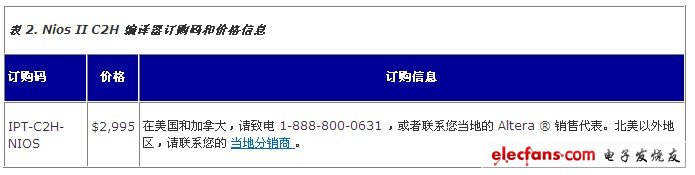

订购信息

您现在就可以订购 Nios II C2H 编译器。请参考表 2 的价格和订购信息。可以下载并免费评估Nios II 嵌入式设计套装(EDS)。 请联系您当地的 Altera 销售代表,了解详细信息。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)