1前言

印制电路板(PCB)信号完整性是近年来热议的一个话题,国内已有很多的研究报道对PCB信号完整性的影响因素进行分析,但对信号损耗的测试技术的现状介绍较为少见。

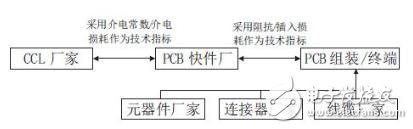

PCB传输线信号损耗来源为材料的导体损耗和介质损耗,同时也受到铜箔电阻、铜箔粗糙度、辐射损耗、阻抗不匹配、串扰等因素影响。在供应链上,覆铜板(CCL)厂家与PCB快件厂的验收指标采用介电常数和介质损耗;而PCB快件厂与终端之间的指标通常采用阻抗和插入损耗,如图1所示。

图1 PCB材料及组装的部分技术指标

针对高速PCB设计和使用,如何快速、有效地测量PCB传输线信号损耗,对于PCB设计参数的设定和仿真调试和生产过程的控制具有重要意义。

2 PCB插入损耗测试技术的现状

目前业界使用的PCB信号损耗测试方法从使用的仪器进行分类,可分为两大类:基于时域或基于频域。时域测试仪器为时域反射计(TIme DomainReflectometry,简称TDR)或时域传输计(TImeDomain Transmission,简称TDT);频域测试仪器为矢量网络分析仪(Vector Network Analyzer,简称VNA)。在IPC-TM650试验规范中,推荐了5种试验方法用于PCB信号损耗的测试:频域法、有效带宽法、根脉冲能量法、短脉冲传播法、单端TDR差分插入损耗法。

2.1频域法

频域法(Frequency Domain Method)主要使用矢量网络分析仪测量传输线的S参数,直接读取插入损耗值,然后在特定频率范围内(如1 GHz ~ 5 GHz)用平均插入损耗的拟合斜率来衡量板材合格/不合格。

频域法测量准确度的差异主要来自校准方式。根据校准方式的不同,可细分为SLOT(Short-Line-Open-Thru)、MulTI-Line TRL(Thru-Reflect-Line)和Ecal(Electronic calibraTIon)电子校准等方式。

SLOT通常被认为是标准的校准方法,校准模型共有12项误差参数,SLOT方式的校准精度是由校准件所确定的,高精度的校准件由测量设备厂家提供,但校准件价格昂贵,而且一般只适用于同轴环境,校准耗时且随着测量端数增加而几何级增长。

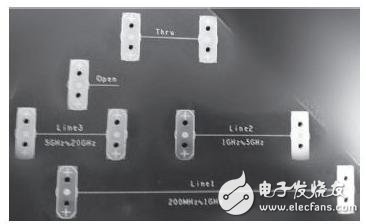

Multi-Line TRL方式主要用于非同轴的校准测量,根据用户所使用的传输线的材料以及测试频率来设计和制作TRL校准件,如图2所示。尽管Multi-Line TRL相比SLOT设计和制造更为简易,但是Multi-Line TRL方式校准耗时同样随着测量端数的增加而成几何级增长。

图2 Multi-line TRL校准件

为了解决校准耗时的问题,测量设备厂家推出了Ecal电子校准方式,Ecal是一种传递标准,校准精度主要由原始校准件所确定,同时测试电缆的稳定性、测试夹具装置的重复性和测试频率的内插算法也对测试精度有影响。一般先用电子校准件将参考面校准至测试电缆末端,然后用去嵌入的方式,补偿夹具的电缆长度。如图3所示。

图3 VNA Ecal方式校准图和测试示意图

以获得差分传输线的插入损耗为例,3种校准方式比较如表1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)