让我们通过一个具体例子来看看地d脉冲到底会有多大。

例:地d的测量

为了这一测量我们将使用一个四触发器,通过配置,使它输出中的3个处于触发状态,而第4个输出固定保持为零。我们可以使3个有交输出中的任何一个都能够通过开关连接到20PF的负载。这个实验配置能分别显示出无负载和重负载的情况下的地d。

因为非触发的第4个输出保持在逻辑LO状态,适合作为探测芯片内部的窗口,我们可以通过它测量内部的地电压。

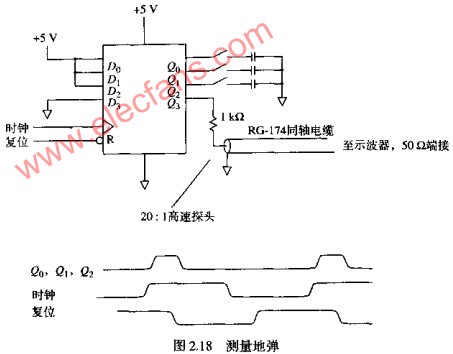

图2.18描绘了这种结构。时钟和异步复位线交替地位置和复位三个有效输出,对于这个实验,我们使用74HC174触发器。

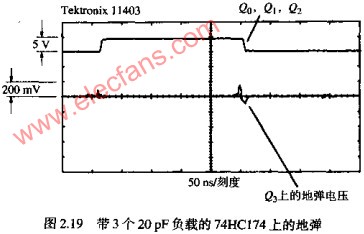

通过连接所有的3个负载,可以得到图2.19的波形。当Q输出跳变为HI。对于这个实验,我们使用74HC174触发器。

通过连接所有的3个负载,可以得到图2.19的波形,当Q输出跳变为HI,跳变电流流入器件内部,相应地出现一个小VGND电剌。当Q输出跳变为LO,出现了大的地d脉冲。在本例中,大约有150MV

一个仅有150MV的脉冲看起来可能不是很大,但是要考虑到以下的因素:

1、HCT逻辑系列的低电平容限只有470MV。

2、如果有8个输出同时跳变,脉冲将会增大至8/3倍。

地d减少了用于补偿其他噪声及信号失真影响的有效剩余噪声容限。

用同样的测量方法在74F174触发器上得到的结果是400MV的地d。

本文地址:https://www.elecfans.com/arTIcle/analog/2010/20100602218828.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)