为了对地d进行有效的预测,需要知道4个要素:逻辑器件的10~90%转换时间,负载电容或电阻,引脚电感和转换电压。

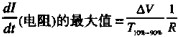

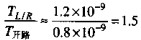

对于一个阻性负载R,可以用式: 得到的电流变化率以及由式:

得到的电流变化率以及由式: 定义的电感来计算地d的幅值:

定义的电感来计算地d的幅值:

对于一个容性负载C,可以用由式 得到电流变化率以及由式定义的电感,来计算地d的幅值:

得到电流变化率以及由式定义的电感,来计算地d的幅值:

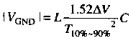

参数△V和T10%~90%的大小取决于逻辑产品系列的数据指标,这里指的是典型值。

表2.2比较了5种逻辑系列产品的转换特性参数:SIGNETICS 74HCT CMOS,TEXAS INSTRUMENTS 74AS TTL,MOTOROLA 10KH ECL,GIGABIT LOGIC 10G GAAS和NEL GAAS。

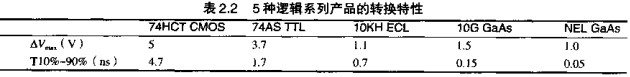

能够显著减少引起电感的最有希望的3种技术分别是丝焊(WIRE BOND),载带自动焊和倒装焊。这3种技术都短缩了芯片和印刷电路板之间的地线连接,参见图2.20。

丝焊法是将一个未密封的管芯背向放置在印刷电路板上,然后在芯片焊盘和印刷电路板上之间焊接上细小的连接引线。芯片及引线随后由一滴被覆材料封闭起来,或者用一个气密外壳密封覆盖整个电路板。

丝焊是一处可机械化 *** 作的简单方法,无论芯片焊盘的定位还是印刷电路板布线方面,都能允许大的变动。丝焊也可以通过手工 *** 作完成较小批量的生产。

载带自动焊用批量端接技术代替丝焊。首先把用于连接芯片到印刷电路板的互连线印制在非常薄的柔性基底上。这个基底工可能有多个层,包括一个用于阻抗控制的地层焊料随后被放置在芯片焊盘处,世芯片通过回流焊焊接到柔性电路上。现在芯片正面已经与柔性电路焊接在一起。下一步,将芯片与柔性电路的组合体用回流焊接法装配到印刷电路板上。最后用一滴被覆材料密封,或者用一个气密外壳密封覆盖整个电路板。

载带自动焊法作为一种大规模装配技术,发展非常迅速。它的优势必在于给所有的信号提供了一个连续的接地平面,而且还提供了芯片和印刷电路板之间的某种机械一致性。载带自动焊法能适应0.08MM这么小的引脚间距。它的缺点是每种芯片都需要一个专门的柔性电路,而且无论是印刷电路板还是芯片引线的改变,都必须要改变柔性电路。

倒装焊接技术首先在芯片在每个焊盘上放置小的焊锡球,然后将芯片面向印刷电路板放置,并立即通过回流焊焊接在相应位置。倒装芯片技术通常用于陶瓷多芯片模块,并附带有先进的冷却结构和完全密封的整体封装。

电气特性方面,倒装芯片技术是非常理想的,焊接引线长度非常小,因此所有和封装有关的寄生产物也都最小化了。而在机械装配和散热方面,芯片倒装技术是极糟糕的,除了焊锡球自身有限的d性以外,在芯片和印刷电路板之间几乎没有任何的机械配合柔性,芯片和印刷电路板之间的热膨胀系数还必须非常紧密地匹配。

因为芯片基底离开了印刷电路板,倒装芯片冷却的问题更加恶化。在丝焊和载带焊法方法中,芯片的装配都是使它的背面与印刷电路板接触,而印刷电路板正好是一个好的散热渠道。

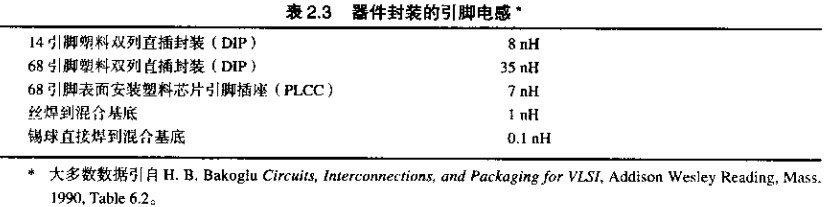

对于各种不同的封装,表2.3列出了其典型的引脚电感值。

本文地址:https://www.elecfans.com/arTIcle/analog/2010/20100602218829.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)