摘要:设计了一种支持IEEE754浮点标准的32位高速流水线结构浮点乘法器。该乘法器采用新型的基4布思算法,改进的4:2压缩结构和部分积求和电路,完成Carry Save形式的部分积压缩,再由Carry Look-ahead加法器求得乘积。时序仿真结果表明该乘法器可稳定运行在80M的频率上,并已成功运用在浮点FFT处理器中。

1 引言

在数字化飞速发展的今天,人们对微处理器的性能要求也越来越高。作为衡量微处理器 性能的主要标准,主频和乘法器运行一次乘法的周期息息相关。因此,为了进一步提高微处 理器性能,开发高速高精度的乘法器势在必行。同时由于基于IEEE754 标准的浮点运算具 有动态范围大,可实现高精度,运算规律较定点运算更为简捷等特点,浮点运算单元的设计 研究已获得广泛的重视。 本文介绍了 32 位浮点乘法器的设计,采用了基4 布思算法,改进的4:2 压缩器及布思 编码算法,并结合FPGA 自身特点,使用流水线设计技术,在实现高速浮点乘法的同时,也 使是系统具有了高稳定性、规则的结构、易于FPGA 实现及ASIC 的HardCopy 等特点。

2 运算规则及系统结构

2.1 浮点数的表示规则

本设计采用单精度IEEE754 格式【2】。设参与运算的两个数A、B 均为单精度浮点数, 即:

2.2 浮点乘法器的硬件系统结构

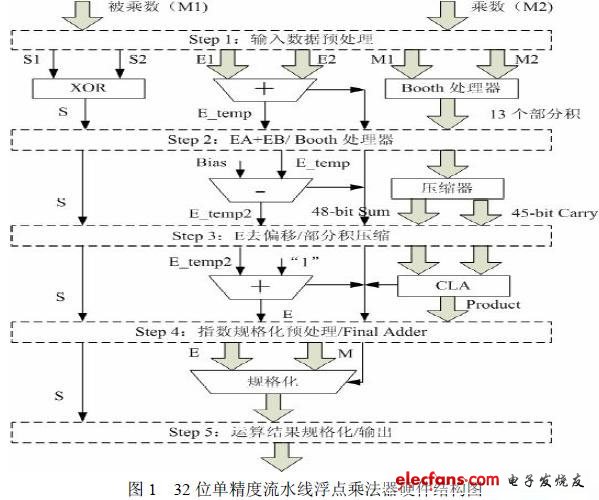

本设计用于专用浮点FFT 处理器,因此对运算速度有较高要求。为了保证浮点乘法器 可以稳定运行在80M 以下,本设计采用了流水线技术。流水线技术可提高同步电路的运行 速度,加大数据吞吐量。而FPGA 的内部结构特点很适合在其中采用流水线设计,并且只需 要极少或者根本不需要额外的成本。综上所述,根据系统分割,本设计将采用5 级流水处理, 图1 为浮点乘法器的硬件结构图。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)