第一部分探究基本拓扑和Σ-ΔADC的功能。

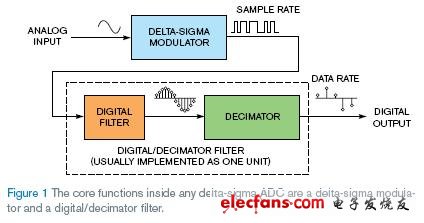

Σ-Δ转换器在从直流到几MHz信号的宽频率范围内,都能理想的实现高分辨率信号转换。图1显示了Σ-ΔADC的基本拓扑或核心,其内部为Σ-Δ调节器和数字滤波器的串联。研究Σ-ΔADC时,可以发现虽然它们具有多种特色,但都为这种基本架构。这个窗和后面的三个Baker最佳窗研究了基本拓扑和这两个模块的功能。

Σ-ΔADC的输入信号为交流或直流电压。这个和后三个Baker最佳窗使用单周期正弦波作为输入信号。使用1位内部ADC,图1中内部转换调节器采集输入信号,产生粗量化的输出作为输入信号。调节器将模拟输入信号转换为高速脉冲波形。调节器输出脉冲序列一到零的比例反映了输入模拟电压。虽然调节器产生一个带噪声的输出,但是未来的列说明电路将噪声“塑造”成更高频率的输出频谱。这个动作为数字滤波器输出的低噪声、高分辨率转换铺平了道路。

在调节器输出,数字滤波器解决了高频噪声和高速采样率的问题。因为信号位于数字域,可以采用低通数字滤波器削弱高频率噪声,采用抽取滤波器减小输出数据的速度。数字/抽取滤波器采样和滤除调节器1位代码串,并创建低速多位编码。

虽然大多数转换器只有一个采样率,Σ-Δ转换器却有两个:输入采样率和输出数据率。这两个有意义的变量比例定义了系统抽取比例。抽取率和转换器有效分辨率之间存在一个强大的关系。未来的窗将检测调节器、数字/抽取滤波器和可调节抽取比例怎样工作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)