ADC 设计的最新进展极大地扩展了可用输入范围,这样系统设计人员便可以去掉至少一个中间频率级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比 (SNR) 的主要原因。本文章重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与ADC 的孔径抖动组合。

采样过程回顾

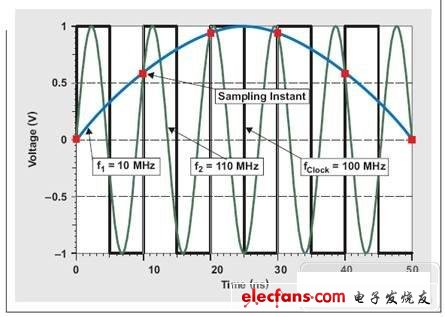

根据 Nyquist-Shannon 采样定理,如果以至少两倍于其最大频率的速率来对原始输入信号采样,则其可以得到完全重建。假设以 100 MSPS 的速率对高达 10MHz 的输入信号采样,则不管该信号是位于 1 到 10MHz 的基带(首个Nyquist 区域),还是在 100 到 110MHz 的更高 Nyquist 区域内欠采样,都没关系(请参见图 1)。

图 1 100MSPS 采样的两个输入信号显示了混叠带来的相同采样点

在更高(第二个、第三个等)Nyquist 区域中采样,一般被称作欠采样或次采样。然而,在 ADC 前面要求使用抗混叠过滤,以对理想 Nyquist 区域采样,同时避免重建原始信号过程中产生干扰。

时域抖动

仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。另外,图 2 表明时钟信号自身转换速率对采样时间的变化产生了影响。转换速率决定了时钟信号通过零交叉点的快慢。换句话说,转换速率直接影响 ADC 中时钟电路的触发阈值。

图 2 时钟抖动形成更多快速输入信号振幅误差

如果 ADC 的内部时钟缓冲器上存在固定数量的热噪声,则转换速率也转换为计时不准,从而降低了 ADC 的固有窗口抖动。如图 3 所示,窗口抖动与时钟抖动(相位噪声)没有一点关系,但是这两种抖动分量在采样时间组合在一起。

图3 ADC的窗口抖动

图3还表明窗口抖动随转换速率降低而增加。转换速率一般直接取决于时钟振幅。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)