本文根据光纤接入数位中频系统的时钟使用情况,分析时钟抖动对类比数位转换器(ADC)和相位锁定回路(PLL)性能影响的塬理,包括相位锁定回路基本原理和相位杂讯优化方式,最后提出采用双相位锁定回路完成去抖和时钟分发的解决方案。

无线射频远端装置(RRU)、数位光纤直放站等常见的数位中频系统,其设备中的时钟讯号多从近端通过光纤传输过来。由于光纤传输的色散影响,原有时钟参考讯号在通过光口晶片后,其抖动指标会恶化。而在远端设备中,这个时钟讯号将会做为整个系统的参考时钟,包括ADC、数位类比转换器(DAC)、调製器和相位锁定回路等。如果这个参考时钟讯号的抖动性能不佳,将会造成系统中上述元件的性能恶化,所以在光纤接入的数位中频系统中,时钟抖动设计非常重要。

时钟相位杂讯影响ADC性能

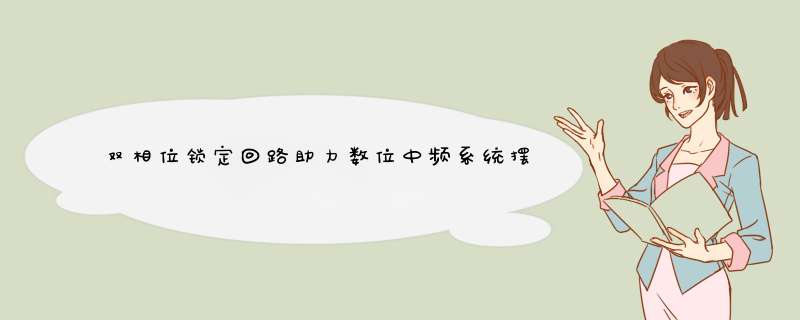

讯噪比(SNR)是数位中频系统中的ADC受关注的指标,这个指标会影响系统的动态范围。一般设计好的高速ADC,其SNR则固定。比如AD6649在95MHz频宽和245.76MSPS的取样速率条件下,SNR为73.4dBFs。这个指标的前提是ADC的参考时钟抖动指标非常好,如果系统提供给ADC的时钟抖动不好,则会恶化实际SNR水准(图1)。

图1 实际SNR取决于系统工作频率和时钟抖动

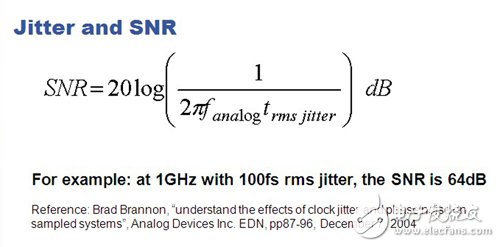

为什么会出现上述现象?如图2所示,采样时钟的抖动在输入讯号投影误差的大小会随着采样时钟自身抖动增加而增加;同时,如果输入讯号的速率(或频率)增加,其瞬态斜率也会增加,那么投影误差也会相应增加。图2亦解释图1公式的原因,所以对于数位中频系统的ADC须要提供优异的时钟讯号,特别是输入中频愈高时,愈须要考虑这个问题。

图2 采样时钟的抖动在输入讯号投影误差的大小会随着采样时钟自身抖动增加而增加。(a表示ADC的采样时钟波形,b则表示一个输入类比讯号的瞬态截图。c表示採样的误差范围。)

到底需要多小的抖动才能够满足系统的ADC需求?不同输入频率,在不同抖动水准下,可以达到不同的最大SNR水准。举例来说,当输入频率为200MHz,系统时钟抖动为200fs水准时,可以达到72dB的SNR水準。

为方便工程师衡量系统受抖动影响SNR的水准,已有业者提供线上ADC性能模拟软件。工程师透过该软件可以选择ADC型号后,输入时钟的抖动水准,以得出SNR实际水准和杂散无杂讯动态范围(SFDR)水準。

时钟对相位锁定回路影响分析

在数位中频系统中,参考时钟还会提供给相位锁定回路做为输入参考频率。相位锁定回路的相位杂讯好坏会影响到接收链路的误差向量幅度(EVM),这是因为输入参考频率的近端相位杂讯进入相位锁定迴路后,并不会被相位锁定迴路的低通滤波器抑制,而会影响到相位锁定回路输出的近端相位杂讯水準,故近端相位杂讯系统是接收机EVM指标的主要影响因素。比较两个不同参考相位杂讯对于同一个相位锁定迴路晶片的近端相位杂讯影响,由于相位锁定回路的参考时钟近端相位杂讯不同,可以发现1kHz频率处,相位杂讯分别为-96dBc/Hz和-89dBc/Hz。

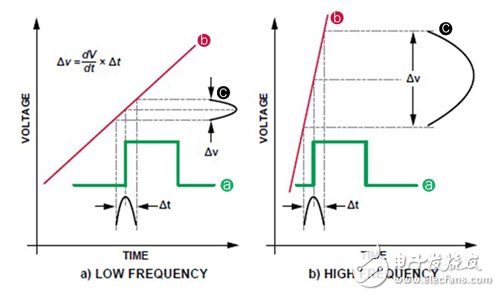

根据相位锁定回路输出的相位杂讯(抖动)水准和输出频率,可以计算其对系统EVM的影响水準(图3)。因此可以得出结论--参考时钟相位杂讯影响相位锁定回路近端相位杂讯、相位锁定回路近端相位杂讯影响系统接收机EVM指标。

图3 计算PLL输出的相位杂讯水准和输出频率对系统EVM的影响水准。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)