理解不同类型的时钟抖动

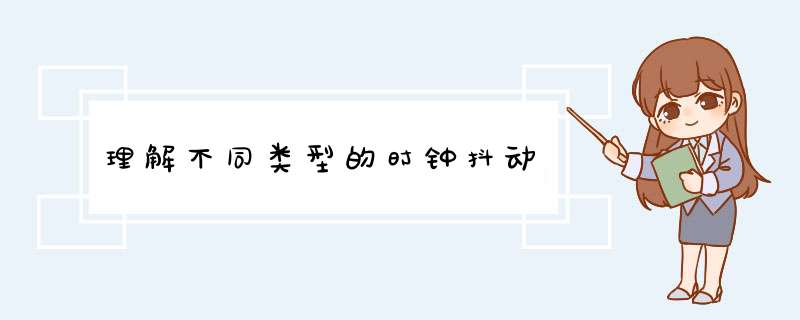

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误差(TIE)抖动、相位噪声及相位抖动。

时钟抖动简介

时钟抖动是时钟沿距离其理想位置的偏离。在应用中理解时钟抖动非常重要,因为它在系统时序预算方面肩负关键角色。它还能帮助系统设计人员理解系统时序余量。随着系统数据率越来越高,时序抖动在系统设计中已经变得更加关键,如在某些案例中系统性能限制由系统时序余量来确定,因此充份了解时序抖动在系统设计中变得更加重要。总抖动可分为随机抖动和确定性抖动等分量。本文并不探讨抖动的组成,而把重点放在时钟抖动的不同类型。时钟时序抖动可以在时域以及频域测量。相邻周期抖动、周期抖动及时间间隔误差(TIE)抖动在时域测量,而相位噪声和相位抖动在频域测量。部分抖动源包括热噪声、电源噪声、地d噪声(ground bounce)、锁相环(PLL)电路、串扰及反射。图1为时钟抖动示例。

图1: 时钟抖动示例。

时钟抖动的不同类型

(1)相邻周期抖动 :测量的是1,000个时钟周期内任意2个相邻时钟周期之间的时钟周期(clock period)变化。

? 相邻周期抖动均方根值(RMS)——测量1,000个时钟周期内任意2个相邻时钟周期之间的时钟周期测量值偏离。

? 相邻周期抖动峰-峰值——测量的是1,000个时钟周期内任意2个相邻时钟周期间的最小时钟周期变化与最大时钟周期变化之差。

相邻周期抖动测量用于确定应用中的高频抖动,因为它测量了两个相邻时钟周期之间的抖动。获得较小的逐周期抖动值非常重要,因为它影响系统时序余量。

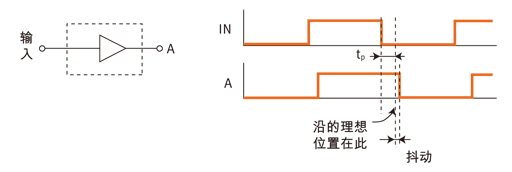

(2)周期抖动:周期抖动测量的是10,000个时钟周期波形内某个时钟周期的时钟周期最大偏离。

? 周期抖动均方根值—— 测量10,000个时钟周期内时钟周期测量值的标准偏离。

? 周期抖动峰-峰值 – 测量的是10,000个时钟周期内最小时钟周期与最大时钟周期测量值之差。

周期抖动测量用于确定应用的低频抖动,因为它藉测量10,000个时钟周期内的时钟周期偏离来测量抖动。周期抖动用于计算系统时序余量。图2是森美半导体可编程时钟NB3N3020的周期抖动测量示例。

图2: 安森美半导体可编程时钟NB3N3020的周期抖动测量示例:

安森美半导体的可编程时钟NB3N3020拥有极佳的可编程时钟抖动性能,典型周期抖动均方根值为3皮秒(ps)。

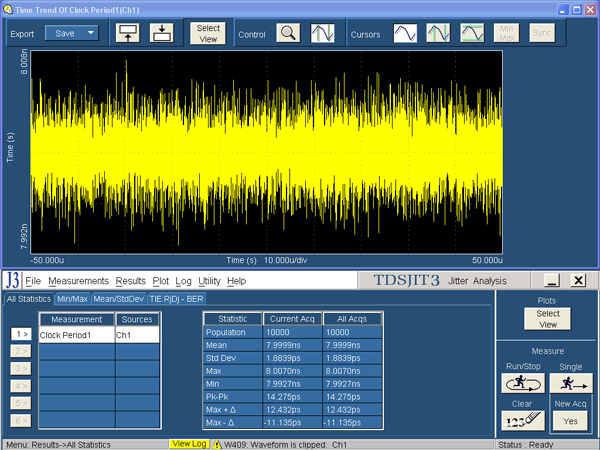

(3) 时间间隔误差(TIE)抖动

时间间隔误差或TIE抖动测量的是时钟每个工作沿(active edge)与相应理想时钟沿的距离。

* 时间间隔误差(TIE)抖动均方根值——测量时序误差的标准偏离

* 时间间隔误差(TIE)峰-峰值——测量最小与最大时序误差之差

时间间隔误差抖动对时钟及数据恢复(CDR)PLL很重要,它显示CDR中的PLL是否能够追踪涌入的数量流。时间间隔误差抖动较大就表明该CDR PLL无法恰当地追踪涌入数据流的变化。图3是安森美半导体NB3N3002时钟产生器TIE抖动测量示例。

图3:安森美半导体NB3N3002时钟产生器TIE抖动测量示例:

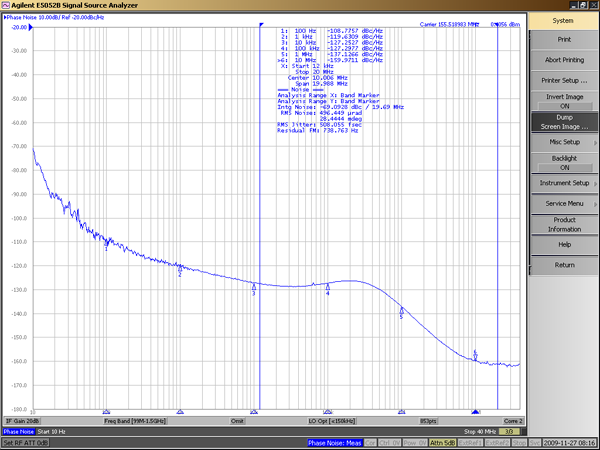

(4)相位噪声:相位噪声在频域测量,是在给定载波信号偏移条件下额定1Hz带宽处的信号功率与噪声功率之比值。安森美半导体的时钟产品拥有极佳的相位噪声性能,如NB3N3002/NB3N5573时钟产生器具有下述相位噪声性能:

Offset Noise Power

100Hz -103dBc/Hz

1kHz -118dBc/Hz

10kHz -122dBc/Hz

100kHz -130dBc/Hz

1MHz -132dBc/Hz

10MHz -149dBc/Hz

相位抖动:相位抖动是藉载波信号特定频率偏移范围内对相位噪声积分来测量的。相位抖动测量的是与载波信号总能量相对应的载波信号特定频率偏移中的能量,测量方式是对相位噪声图下的面积进行积分。例如,同步光网络(SONET)使用距离载波信号有12kHz至20MHz的频率偏移,对相位噪声图下的面积积分,从而测量相位抖动。光纤信道(FC)则使用距离载波信号637KHz到10MHz的频率偏移来对相位噪声图下的面积积分,从而测量相位抖动。

相位噪声及相位抖动测量示例

安森美半导体的PureEdge PLL的典型相位抖动低于0.5ps。图4的相位噪声图显示了安森美半导体晶体振荡器产品系列中的一款PureEdge PLL器件NBXDBA018的性能。这器件产生155.52MHz/311.04MHz的双频低压正射极耦合逻辑(LVPECL)输出,满足SONET应用的抖动要求。

图4:相位噪声图显示安森美半导体PureEdge PLL的典型相位抖动低于0.5ps。

总结:

本文介绍了时钟抖动并阐释了时钟抖动的不同类型以及各种类型时钟抖动测量的意义。本文还给出了不同类型时钟抖动测量的示例。随着系统数据率增高,有时候系统性能限制由系统时序余量确定,因此,理解时序时钟抖动对系统设计人员很重要。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)