编者语:笔者本科专业电子信息工程,读书时代用的第一块开发板就是Altera公司的,当时脑子里完全没有Altera这个概念,只知道这是块FPGA开发板。但就是这块开发板让我开始接触并深刻认识到FPGA技术、VHDL语言的魅力。虽然后来没去钻研做技术,但它给我留下的印象是最深刻的。那么,各位自称FPGA工程师的你们是不是也一样呢?Altera公司的FPGA开发板用了那么多年,Quartus II 软件用得那么顺手。但是却不了解“Altera这家伙到底是什么呢?“、”它多大了?“、”它为什么能在中国这片广阔天地上培育出这么多牛叉的工程师?“...笔者在跟很多FPGA工程师聊天的过程中,经常会听到这些疑问。凑巧Altera今年30周岁,笔者就带着大家一起来见识下Altera的30年发展历程吧...

创始年代

1983年,Altera公司正式成立。很多人现在对这一年印象还非常深刻——挑战者号和哥伦比亚号航天飞机首航,菲律 宾总统小阿基诺被暗杀,美国入侵格林纳达等。而在技术领域却是白驹过隙,30年显得如此漫长。TCP/IP成为ARPANET的正式协议——那时还没有互 联网。IBM推出了PC-XT——个人计算机还没有硬盘。宣布了GNU项目。

在电子设计领域,微处理器在很多嵌入式设备中得到了广泛应用,替代了高端微型计算机,在低端则替代了大量的小规模数字芯片。典型的数字系统包括微处理器或 者微控制器,周围是接口电路,连接芯片总线和外部存储器芯片以及接口。小规模逻辑芯片和中等规模功能模块IC还在使用,更多的用在建立微处理器周围的接 口,或者桥接总线,对于性能关键的应用,则协助微处理器完成一些 *** 作。

而且,这一时期,在设计领域逐渐采用了新的替代解决方案。逻辑门阵列——特别是经过预制造的逻辑门阵列,在最终产品阶 段,由一系列客户定义的金属层进行配置,支持设计人员将数千个逻辑门和存储器封装到一个芯片中。对于很多项目,并不熟悉设计过程,依靠于基于工作站的 EDA工具进行原理图采集,获取库单元,进行仿真,而前端费用非常昂贵。但是对于规模较大、资金较充裕的设计团队,逻辑门阵列是很好的替代方案,减少了芯 片数量,提高了设计性能,同时降低了功耗。

从今天的标准来看,那时的设计风格也是千差万别。习惯于数字逻辑的工程师通常使用形式结构来进行设计:布尔代数和最小表 达式定义组合逻辑,通过状态机来描述时序逻辑。这些工程师会使用手动方法或者越来越多的计算机软件工具来采集并分析其设计。但是工程师的背景各不相同,特 别是模拟工程师,通常会使用更直观的方法。这些设计人员倾向于使用原理图进行设计输入,从左侧的空白开始设计,然后是输入信号到输出,增加逻辑门、触发 器、中等规模的器件,以及要连接的微处理器。逻辑门阵列用户也倾向于采用原理图方法,这只是因为它能够对在芯片中建立的电路进行近似描述。这两种相反的设 计风格在设计发展过程中都扮演了一定的角色,但是业界在1983年出现了另一种创新方法,并逐渐得到广泛应用。

1978年,出现了另一种替代方法,但还没有引起重视。Monolithic Memories的芯片设计团队开发了一款名为PAL的器件(对于“可编程阵列逻辑”,采用了更知名的术语“可编程逻辑阵列”)。芯片是一次性编程数字器 件,实现布尔表达式的简化标准形式:乘积求和格式。PAL含有很多宏单元,每个单元包括开关阵列,这可以将芯片的任意输入和输出连接至8个乘积项中的每一 个。然后,宏单元在宽OR逻辑门中对乘积项进行求和,提供可配置触发器,寄存OR逻辑门的输出,为选择时钟提供一些复用器,旁路寄存器,等等。1983 年,PAL的容量、速度和配置发展很快,使得设计人员有很大的选择余地。

这些可编程器件为数字设计人员提供了很好的方法:逻辑密度高于小规模逻辑门和触发器,比专用商用中等规模器件更灵活,例 如,计数器、寄存器和解码器,与逻辑门阵列相比,还提供非常熟悉的设计流程,没有前端开支。供应商为微型计算机和大型机提供软件工具,这可以转换成布尔表 达式、状态机,某些机制转换为芯片开关映射。

Altera登场

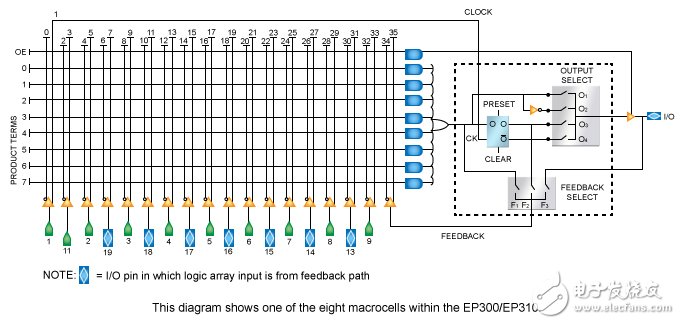

这是Altera于1984年推出其首款产品的环境。EP300芯片( 图1)是可编程逻辑芯片,但是在四个方面与PAL有明显的不同。首先,EP300是可重新编程的,看起来比较方便,而事实表明这成为了业界的关键因素。封装上的石英窗口支持用户对管芯进行紫外灯照射,擦除含有器件配置的EPROM单元,因此,可以再次对芯片进行编程。

图1.通过管芯上的窗口,照射紫外光,Altera EP300具有可擦除能力。

其次,EP300是CMOS器件,那时,还是采用高功耗的双极工艺来制造大部分PAL、小规模和中等规模逻辑。第 三,Altera芯片是通用的——即,用户可以对EP300进行编程,几乎可以模拟绝大部分现有PAL类型器件的配置。最后,Altera为EP300提 供了设计工具,这一工具运行在IBM PC上,而不是工程工作站或者微型计算机上。Altera资深副总裁Don Faria回忆说:“这的确是创新。PC刚刚出现,工程师对其很有兴趣,有时候,人们观看我们的演示就是为了看一看PC-XT。”

还有另一点不同,是与Altera有关,不仅仅是EP300。Altera采用了代工线模式。那时大部分半导体公司都依 靠他们自己生产线的专用工艺来获得竞争优势,Altera设计的EP300也尽可能采用通用EPROM工艺。因此,可以在很多其他公司生产线上生产芯片, 只需要对设计进行很小的改动即可。石印掩膜就是刀刻红膜相片——只修改设计文件参数并不能改变它。因此,开发的设计要在性能上有竞争力而且可移植性要好, 这的确有一定的难度。

图2.EP300被排列成可配置乘积求和。

通过在EP300中实现接口和状态机,设计人员可以尝试新的逻辑表达式,重新配置设计,重新映射地址总线,以及类似的试 验,不会有PAL各种各样的问题。更重要的是在成本上,这可能不是令人很激动,但他们可以设计一块电路板,在成品中安装各种型号器件,甚至可以在现场进行 重新配置。由于有这些优势,EP300及其衍生型号很快得以广泛应用,设计人员自然会希望将更多的功能在可编程器件中实现。这种趋势促使生产出规模更大的 器件。

越来越多的问题

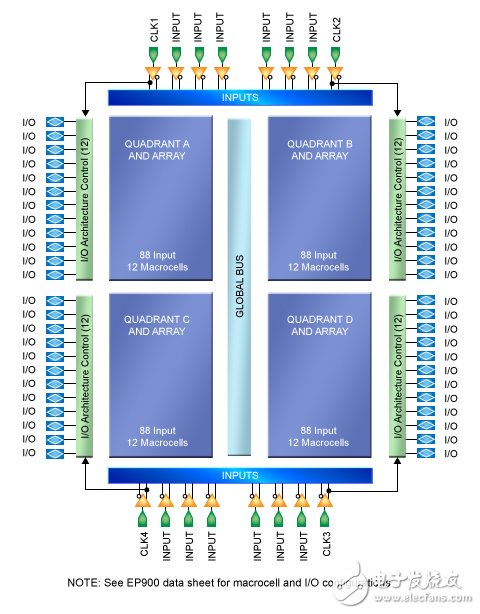

Altera的响应是扩展芯片系列,含有更多的宏单元,最终在EP1800中,68引脚的含铅芯片载体上实现了48个宏 单元器件。在这一点,对逻辑容量的需求对PAL体系结构带来了很大的压力,促使体系结构开始发展变化。Faria解释说:“我们知道标准PAL体系结构很 难进行调整。”

在传统的PAL中,每一宏单元的每个乘积项可以访问所有输入信号,所有宏单元输出,以及所有这些信号的互补信号。随着宏单元数量的增加,这一排列好的互联矩阵会呈几何级数增长,很快将无法承受。Faria说:“因此,我们开始对互联进行划分。”

在EP1800中,这一趋势非常明显,一个封装中实际是四个独立的EP300器件( 图3)。由内部总线将这四个器件连接起来,而不是都尝试去驱动相同的乘积项矩阵。这种组织使得器件具有可制造性,但是,要求设计人员要想清楚哪一宏单元去实现某一逻辑表达式,其他的哪一宏单元要访问结果。器件四个部分的连接会带来额外的延时。

图3.随着可编程器件容量的增长,简单的乘积求和组织被划分设计替代,并不是所有的乘积项要访问所有信号。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)