一直都在System Generator下做图像处理相关的算法,感觉SysGen挺强大的,前几天突发奇想,能否直接用SysGen实现数据的通信呢,毕竟一句HDL代码都不写对于做FPGA的人来说却是很有吸引力的。

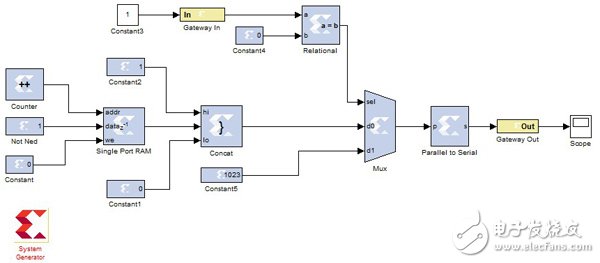

串口通信协议比较简单,发送的时候,8位数据的前面加上1位起始位0,在8位数据后加上停止位1,这样8位数字扩展成10位的数字,再将并行转化为串行就可以从GPIO送出。

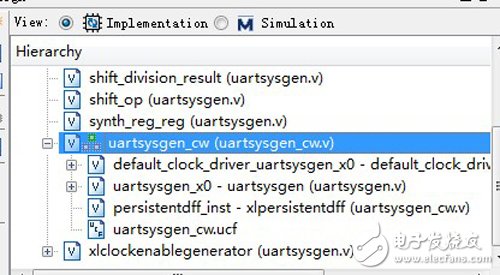

搭建模型如下:

模型因为暂时只是包含发送部分,所以不是很复杂,另外加上一个按键,每次按下按键式就发送数据。

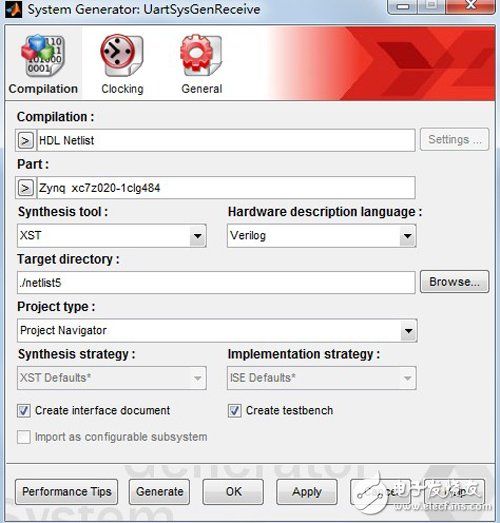

选择板子型号:

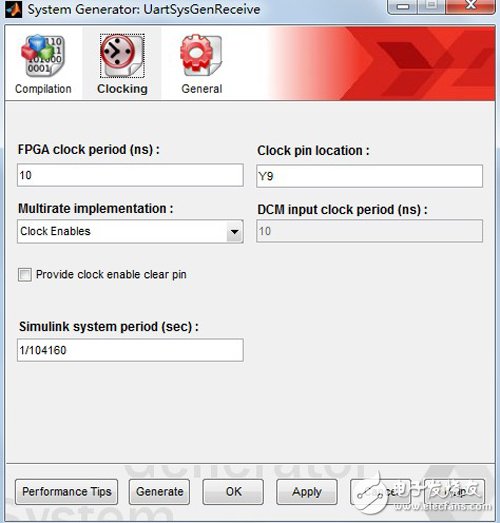

设置时钟:

点击Generate,转化为HDL Netlist,这是会在文件夹下多出一个文件夹,里面有一个ISE工程,使用ISE打开,修改UCF文件。

NET "clk" LOC = Y9 | IOSTANDARD=LVCMOS33; # "GCLK"

NET "ce" LOC = P16 | IOSTANDARD=LVCMOS18; # "BTNC"

//NET "rxd" LOC = Y11 | IOSTANDARD=LVCMOS33; # "JA1"

NET "gateway_out[0]" LOC = AA11 | IOSTANDARD=LVCMOS33; # "JA2"

NET "gateway_in[0]" LOC = T18 | IOSTANDARD=LVCMOS18; # "BTNU"

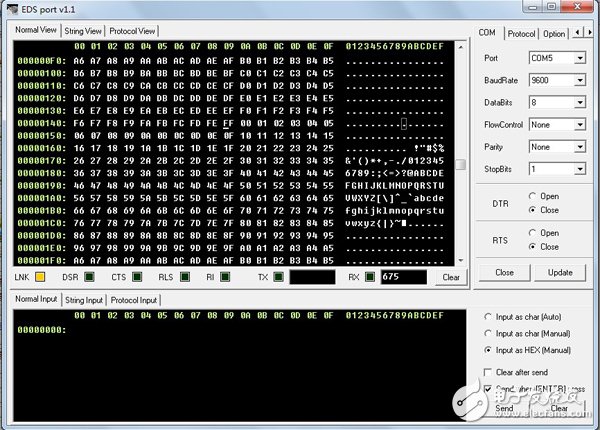

综合布线生成bitstream文件之后,直接下载。按下BTNU就会有数据发出。我在初始化的时候写入的是0->255,在串口助手中也能看到连续的数字。

目前只是实现了串口的发送,毕竟这个相对于接收还是比较简单的,还没想好接收怎么写,先跟大家分享下吧~~

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)