HDL设计和验证与System Generator相结合

Xilinx®SystemGeneratoRForDSP是用来协助系统设计的MATLABSimulink模块集。SystemGeneratorforDSP在熟悉的MATLAB环境中引入XilinxFPGA对象,让您能够对设计进行功能仿真,并且使用MATLAB环境对照理想参考结果验证位精度和时序精度模型。这些参考结果可以在MATLAB环境外部生成,也可以在其内部生成,在这两种情况下您均可从MATLAB环境中引用XilinxFPGA硬件平台。

SystemGenerator为功能仿真和硬件验证提供容易配置的测试平台,以此来辅助完成HDL设计任务。您可以连接ModelSim之类HDL仿真器的内置接口在MATLAB内部仿真HDL代码。围绕HDL代码所构建的SystemGeneratorforDSP测试平台提供强大而快捷的仿真环境,并与ModelSim无缝互动,而且这种环境很容易设置。

我们还可以用同样的环境测试实际硬件中运行的HDL代码,且无需任何修改。硬件协同仿真系统可以使用之前支持的FPGA平台(如XilinxML506开发板)由Simulink来执行单步时钟硬件 *** 作或实时数据突发 *** 作。

CABAC模块的系统化设计和验证

H.264/AVC视频编码器是多年来群策群力的成果,所形成的标准以显著低于以前标准的比特率提供优良的视频品质。开发人员可以使用一种称为H.264/AVCJointModel(JM)的参考C源代码。并且可以用此源代码作为HDL中所实现功能的参考起点。

上下文自适应二进制算术编码(CABAC)是H.264视频标准的组成部分。CABAC模块的功能是用标准通讯组件在HDL中手工转换的。在这种验证中使用最多的组件是FIFO接口。原始JM源代码还可以用来生成模块的测试矢量文件。

我们还构建了另外一种测试环境,它使用JM模型生成CABACHDL模块的输入激励并依据JM参考模型产生的结果来验证HDL的输出结果。这是对传统HDL测试平台基础上的重大改进。

模块验证过程包括以下三个步骤:

1.HDL功能仿真。带有输入和输出测试矢量的MATLAB验证可以分别输入到ModelSim中进行仿真然后比较结果。

2.硬件功能验证。这是一个中间步骤,其目的是找出在HDL功能仿真过程中未发现的所有漏洞。此阶段通过SystemGeneratorforDSP控制单步时钟。在JM源模型生成的文件中我们可以提取输入和输出测试矢量。在SystemGeneratorforDSP中构建文件接口时大家应特别慎重,以防出错。

3.硬件实时验证。使用HDL功能仿真的输入测试矢量以实际的输入速率和时钟输入到硬件中运行,同时采集硬件的输出,并将其输入到MATLAB中与输出测试矢量进行比较。

HDL功能仿真

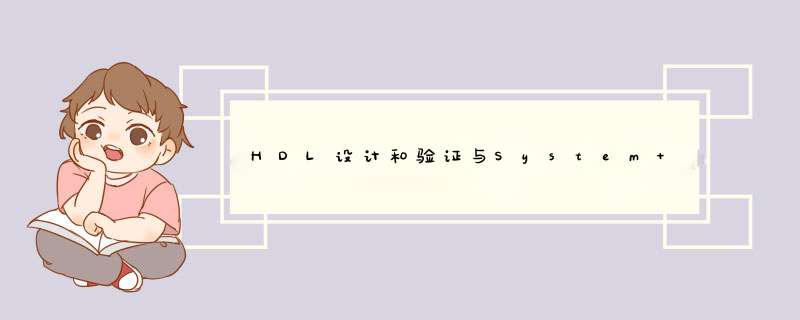

在此步骤中,我们可以将ModelSim仿真与SystemGeneratorforDSP仿真相结合,如图1所示。

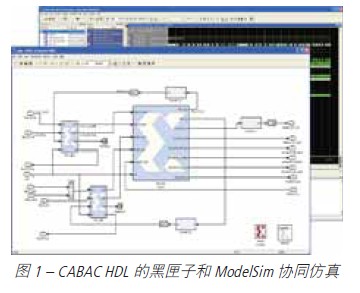

为了在SystemGeneratorforDSP中仿真HDL模块,我们可以通过在边界处插入转换器,以此来创建一个黑匣子来代表VHDL的顶层文件,亦如图1所示。这些转换器将ModelSim的未知“X”状态转换成Simulink仿真中的零。图2所示为整体仿真的测试平台设置。

在图2中,“Slice_inputsubsystem”模块和“MB_inputsubsystem”模块通过使用专用接口代码来读取JM源代码创建的包含激励的文件。“Output_compare”子系统是特殊模块,该模块将仿真的结果与JM源代码产生的原始测试矢量结果进行比较。此仿真是以单步执行的。

使用ChipScope分析器用硬件进行功能仿真

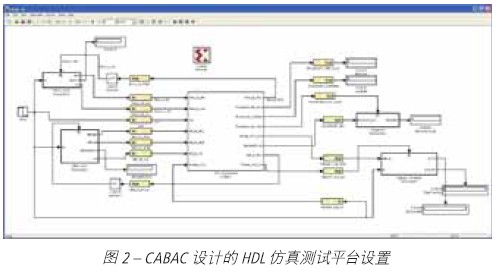

下一步我们可以使用熟悉的环境,在这个环境中将整个HDL模块映射到硬件上,同时还需要带有以太网和JTAG的ML506开发板。以太网连接用来提供并读取激励数据,而JTAG端口则用来连接ChipScope分析器。尽管这给用户的感受是一样的,但现在HDL是完全在硬件中实现。图3所示为系统设置。

这种环境设置的优点是您可以完全从特定接口的细节中抽象出来,而不必再去了解如何用以太网提供输入激励或从CABAC模块中如何读取输出。图3所示专用网关模块就是完全从这些细节中抽象出来的。

实时硬件验证

前述仿真和 *** 作为在时间层上进行模块的详细执行提供了良好的环境。在完整的设计中,我们通常希望使用代表真实测试情况的大型测试集。显然单周期或单步接口 *** 作不适合这种验证方式。

现在,使用与ML506开发板相同的硬件设置,可以用通过一种称为M-HWcosim的新型MATLAB接口所提供的大型数据集进行验证。M-HWcosim是MATLABM文件向硬件传输数据的API。现在,MATLAB脚本编写环境可以向在硬件中运行的实际CABAC模块提供所有数据。

具有流程控制的FIFO允许在运行MATLAB的计算机和全速运行CABAC模块的硬件之间进行异步通讯。这种环境抽象出该接口的细节,在CABAC模块的大型数据集验证中起着重要作用。有关这种环境的详情,请见www.xilinx.com/cn上的白皮书《用SystemGenerator进行系统化HDL设计、验证和鉴定》。

结论

在完整的系统设计中,验证的工作量常常不亚于实际设计。符合H.264标准的CABAC模块设计借助JM源代码模型从高级语言生成测试矢量。其中,HDL设计验证与SystemGeneratoRForDSP和MATLAB相结合。另外,与高速运行CABAC模块的开发板相结合则是对传统环境的重大改进。这显著缩短了构建验证环境所需的时间,从而使您能集中精力于手头的实际模块。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)