当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/CPLD相连接的芯片的工作时钟大多数情形下与FPGA的时钟同源,如果输出的信号经过时钟锁存可以起到如下的作用:

容易满足芯片间信号连接的时序要求;

容易满足信号的建立保持时间;

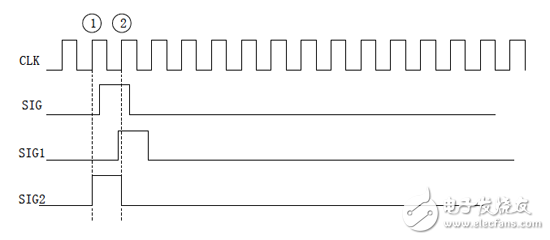

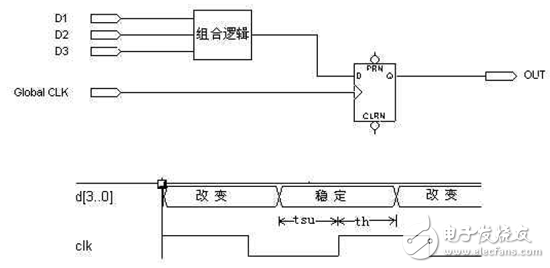

如上图所示,比如FPGA/CPLD在CLK的时钟沿1锁存一个信号得到SIG所示的波形,SIG信号需要给另外的一个与其接口的芯片,那么该芯片将一定会在CLK的时钟沿2正确采样到SIG信号。但是如果该信号在FPGA/CPLD中输出的时候不是用时钟沿锁存的,那将有可能出现SIG1/SIG2所示的时序关系,则与其接口的芯片在时钟沿2处采样该信号的时候有可能出现建立保持时间不满足要求而出现采样不可靠、沿打沿等情况。另外通过组合逻辑输出还有可能出现毛刺的情况。所有这些不规范的设计都会引起系统工作时的不可靠、不稳定的情形。

2.5 寄存异步输入信号我们在日常的设计工作中,FPGA/CPLD总是要与别的芯片相连接的,FPGA/CPLD会给别的芯片输出信号,同时也要处理别的芯片送来的信号,这些信号往往对FPGA/CPLD内部的时钟系统而言是异步的,为了可靠的采样到这些输入信号,建议将这些输入信号使用相应的时钟锁存后在处理,这样做:

将原来的异步信号转化成同步来处理;

去除输入信号中的毛刺(特别是对于数据总线);

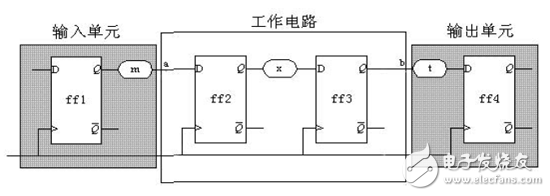

FPGA/CPLD中信号的输入、输出锁存

2.6 FPGA/CPLD中的时钟设计

无沦是用离散逻辑、可编程逻辑,还是用全定制硅器件实现的任何数字设计,为了成功地 *** 作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错误的行为,并且调试困难、花销很大。在设计FPGA/CPLD时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

无论采用何种方式,电路中真实的时钟树也无法达到假定的理想时钟,因此我们必须依据理想时钟,建立一个实际工作时钟模型来分析电路,这样才可以使得电路的实际工作效果和预期的一样。在实际的时钟模型中,我们要考虑时钟树传播中的偏斜、跳变和绝对垂直的偏差以及其它一些不确定因素。

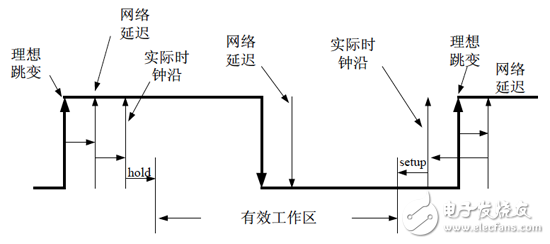

对于寄存器而言,当时钟工作沿到来时它的数据端应该已经稳定,这样才能保证时钟工作沿采样到数据的正确性,这段数据的预备时间我们称之为建立时间(setup TIme)。数据同样应该在时钟工作沿过去后保持一段时间,这段时间称为保持时间(hold TIme)。因此具体的时钟如图5所示。其中网络延迟是指时钟的传播延时以及因为跳变不垂直等效的偏差,在此基础上考虑一些不确定因素实际的工作时钟沿如图中所示。保持时间(hold)和建立时间(setup)都是相对于实际时钟跳变而言的。因此在确定电路时序时,必须要考虑到这些因素,使得建立时间和保持时间符合要求。

图5 工作时钟模型

为了使电路正常工作,建立时间和保持时间应该分别满足:

其中tclock_Q_max是时钟沿变化到数据输出端变化的最慢变化情况,tlogic_max是寄存器间组合逻辑的最大可能延迟,tclock_Q_min和tlogic_min表示最快情况。在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。

2.6.1 全局时钟对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。在PLD/FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟。PLD/FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

图1示出全局时钟的实例。图1定时波形示出触发器的数据输入D[1..3]应遵守建立时间和保持时间的约束条件。建立和保持时间的数值在PLD数据手册中给出,也可用软件的定时分析器计算出来。如果在应用中不能满足建立和保持时间的要求,则必须用时钟同步输入信号(参看下一章“异步输入”)。

图1 全局时钟

(最好的方法是用全局时钟引脚去钟控PLD内的每一个寄存器,于是数据只要遵守相对时钟的建立时间tsu和保持时间th)

2.6.2 门控时钟欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)