2.1 FPGA设计中的同步设计

异步设计不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

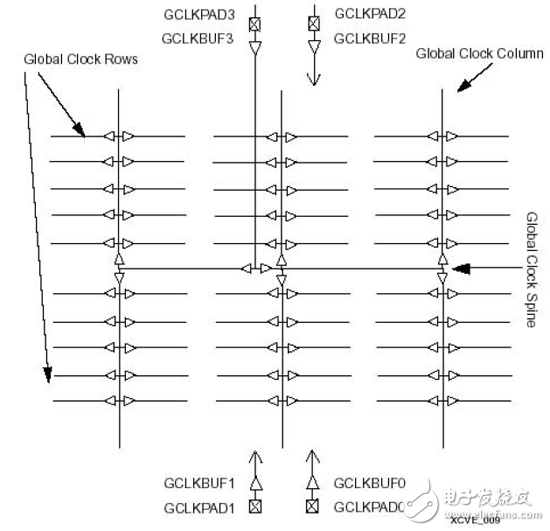

另外,在FPGA的内部资源里最重要的一部分就是其时钟资源(全局时钟网络),它一般是经过FPGA的特定全局时钟管脚进入FPGA内部,后经过全局时钟BUF适配到全局时钟网络的,这样的时钟网络可以保证相同的时钟沿到达芯片内部每一个触发器的延迟时间差异是可以忽略不计的。

在FPGA中上述的全局时钟网络被称为时钟树,无论是专业的第三方工具还是器件厂商提供的布局布线器在延时参数提取、分析的时候都是依据全局时钟网络作为计算的基准的。如果一个设计没有使用时钟树提供的时钟,那么这些设计工具有的会拒绝做延时分析有的延时数据将是不可靠的。

在我们日常的设计中很多情形下会用到需要分频的情形,好多人的做法是先用高频时钟计数,然后使用计数器的某一位输出作为工作时钟进行其他的逻辑设计。其实这样的方法是不规范的。比如下面的描述方法:

process

begin

wait unTIl clk’event and clk=’1’;

if fck=’1’ then

count<=(others=>’0’);

else

count<=count+1;

end if;

end process;

process

begin

wait unTIl count(2)’event and count(2)=’1’ ;

shift_reg<=data;

end process;

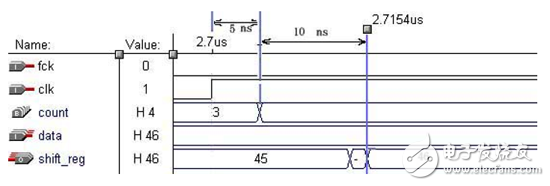

在上述的第一个process电路描述中,首先计数器的输出结果(count(2))相对于全局时钟clk已经产生了一定的延时(延时的大小取决于计数器的位数和所选择使用的器件工艺);而在第二个process中使用计数器的bit2作为时钟,那么shift_reg相对于全局clk的延时将变得不好控制。布局布线器最终给出的时间分析也是不可靠的。这样产生的结果波形仿真如下图所示:

正确的做法可以将第二个process这样来写。

process

begin

wait unTIl clk’event and clk=’1’ ;

if count(2 downto 0)=”000” then

shift_reg<=data;

end if;

end process;

或者分成两步来写:

process(count)

begin

if count(2 downto 0)=”000” then

en<=’1’;

else

en<=’0’;

end if;

end process;

process

begin

wait unTIl clk’event and clk=’1’ ;

if en=’1’ then

shift_reg<=data;

end if;

end process;

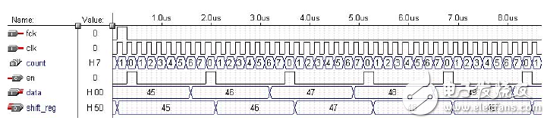

这样做是相当于产生了一个8分频的使能信号,在使能信号有效的时候将data数据采样到shift_reg寄存器中。但此种情形下shift_reg的延时是相对于全局时钟clk的。下面的图形更能看得清楚。

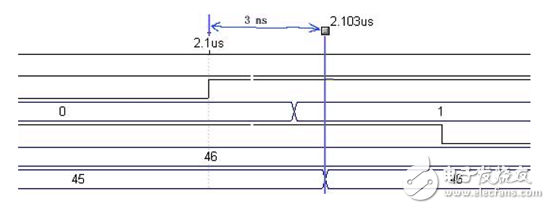

上图中波形的局部放大

2.2 FPGA设计中的延时电路的产生:在日常的电路设计中,有时候我们需要对信号进行延时处理来适应对外接口的时序关系,最经常也是最典型的情况是做处理机的接口;因为与处理的接口时序关系是异步的,而一个规范的FPGA设计应该是尽可能采用同步设计。那么遇到这种情况该如何处理呢?

首先在FPGA中要产生延时,信号必须经过一定的物理资源。在硬件描述语言中有关键词Wait for xx ns,需要说明的是该语法是仅仅用于仿真而不能用于综合的,可综合的延时方法有:

使信号经过逻辑门得到延时(如非门)

使用器件提供的延时单元(如Xilinx公司的);

注意:当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己。

需要说明的是在FPGA/CPLD内部结构是一种标准的宏单元,下图是Xilinx公司的Spartans II系列器件的一个标准宏单元。虽然不同的厂家的芯片宏单元的结构不同,但概括而言都是由一些组合逻辑外加一或二个触发器而构成。在实际应用中,当一个模块内的组合逻辑被使用了那么与其对应的触发器也就不能用了;同样如果触发器单元被用了那么组合逻辑单元也就废了。这就是有时候(特别是使用CPLD)虽然设计使用的资源并不多但布局布线器却报告资源不够使用的原因。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)