在我们用ModelSim仿真的时候经常是修改一点一点修改代码,这样会造成一个无奈的 *** 作循环:修改代码--->编译代码--->仿真设置--->进入仿真页面--->添加需要观察的波形--->运行仿真。如果仿真结果不理想,还得需要重新修改代码,重复上述的 *** 作。

计算机擅长做重复的事情,为什么不让计算机代劳呢?

我们可以参照Xilinx ISE是如何调用ModelSim进行仿真的,尤其是脚本的编写。

下面一个脚本是我用ISE10.1建立了一个AES256的工程,然后在调用ModelSim6.5的时候,ISE会生成这几个脚本文件,AES256_tb.fdo, AES256_tb_wave.fdo 和 AES256_tb.udo。

下面的代码是AES256_tb.fdo文件的内容。

1: vlib work #创建名字是work的库,这个仿真之前必须做的

2: vcom -explicit -93 "SBOX_ROM.vhd" #编译vhd代码

3: vcom -explicit -93 "Inv_SBOX_ROM.vhd"

4: vcom -explicit -93 "AES_package.vhd"

5: vcom -explicit -93 "subbytes.vhd"

6: vcom -explicit -93 "SBOX_ROM_reg.vhd"

7: vcom -explicit -93 "round_key_BRAM.vhd"

8: vcom -explicit -93 "Inv_subbytes.vhd"

9: vcom -explicit -93 "Keyexpansion_Yao.vhd"

10: vcom -explicit -93 "AES256_ENC_DEC.vhd"

11: vcom -explicit -93 "AES256_TOP.vhd"

12: vcom -explicit -93 "AES256_tb.vhd"

13: vsim -t 1ps -lib work AES256_tb #进入仿真设置,时间单位为1ps,库指定为work,AES256_tb就是指你的top层设计的名字

14: do {AES256_tb_wave.fdo} #执行*.fdo文件,用来添加信号和变量或者内部的寄存器到波形(WAVE)窗口

15: view wave #打开波形窗口

16: view structure #打开架构(structure)窗口

17: view signals #打开信号列表窗口

18: run 1000ns #运行1000ns

19: do {AES256_tb.udo} #运行用户定义的脚本

只要编译的时候没有出现语法错误或者是找不到定义的库文件等错误提示,一般会很容易的看到仿真的波形,而不用手动进行 *** 作。这样方便了仿真的整个过程,而无需用很多鼠标点击 *** 作。

现在通过一个具体的实例来说明如何运用脚本来实现ModelSim的仿真。

工具版本:ISE10.1 ,ModelSim 6.5a

1. 创建ISE工程首先通过ISE创建test.vhd 和test_tb.vhd文件并添加到工程中,这里不细说如何创建HDL源代码。

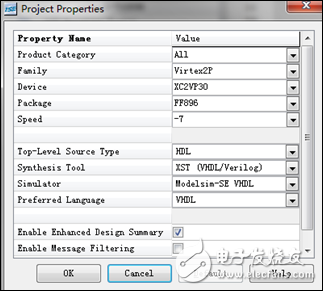

然后配置ISE的仿真器,右键选中FPGA芯片,点击properTIes,然后在Simulator选择Modelsim-SE VHDL。

图1. 工程属性

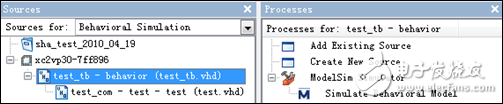

在source窗口选择“Behavioral SimulaTIon”,可以看到工程中的test_tb.vhd(testbench文件)。选中test_tb.vhd文件,在Process窗口中双击Simulate Behavioral Model,ISE开始调用ModelSim,这是ISE自动生成了三个脚本文件:test_tb.fdo, test_tb_wave.fdo和test_tb.udo。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)