上次博文简要介绍了人们研究使用FPGA来进行工业控制的驱动力与FPGA器件与工具的介绍,本次介绍FPGA设计方法论中的FPGA体系及其开发工具介绍。

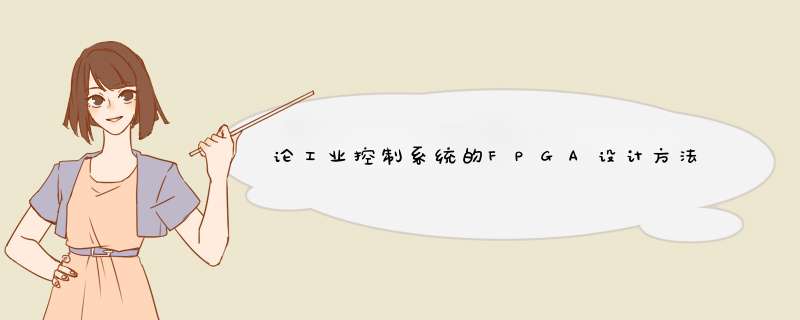

1. FPGA一般体系结构的描述正如FPGA被定义为一个可配置逻辑块(CLB)矩阵,各CLB由互连网络相互关联,且这些模块全部是完全可编程的。存储单元的逻辑控制块以及它们之间的连接允许该组件可以满足特定的应用需要。此外,需要灵活的、可再编程的技术对其进行配置,如FLASH、EPROM、SRAM等,这使得FPGA可以像微处理器具有一样的灵活性。因此,本博文的其余部分将只讨论迄今为止应用最广泛的基于SRAM的FPGA技术。(基于闪存的FPGA技术,虽然不具备词综灵活性,但是一些工作环境恶劣的应用中,如航空航天事业对此有很大的兴趣)。图 1为基于SRAM为基础FPGA 的一般结构()。

最近,在FPGA的结构内部开始引进一些专用模块如RAM,DSP加速(带有累加器的乘法器,高速时钟管理电路,以及串行收发器等),嵌入式硬处理核如PowerPC处理器、ARM处理器,软处理器内核如Microblaze软核。此外,在控制应用中非常有趣的是Actel公司将模数转换集成电路其融合到其FPGA中。尽管这种SoC并没有取代前者的一般结构,但它可以作为原有矩阵块结构的补充。

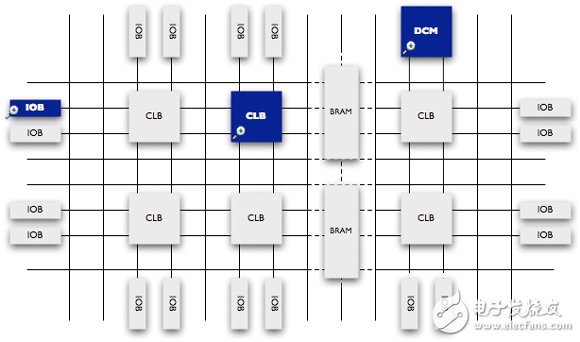

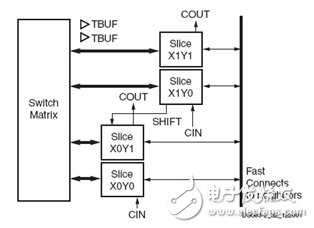

1)可配置逻辑块(CLBs):其结构包括2个、4个或更多的逻辑单元(也称为逻辑元件)。一个逻辑单元结构如图2所示,它是Xilinx FPGA的基本逻辑单元。

B、HDL和FPGA

FPGA发展的初期仅仅用来进行逻辑集成,并且可以用简单的CAD工具对其进行描述;而这在可编程器件出现之前通常由TTL基本逻辑电路来完成。如今, FPGA正用于实现越来越复杂的功能。例如,单个FPGA便可实现一个完整的数字系统,因为其内部往往包含算术逻辑单元(ALU)、存储器、通信单位等许多单元。

这一演变能够在超大规模集成电路的最新进展中找到起源,但它也和某些设计工具和设计方法的发展有关,这些尽管工具一开始是为ASICs设计而提出的。这些工具大多是基于如VHDL或Verilog HDL之上的。IEEE标准的存在使得HDLs语言得到推广,同时使高性能CAD工具在微电子领域得到创造和发展。因此,设计者可以利用HDLs语言通过不同层次的抽象分层和模块化的设计方法,使用“自上而下”的理念,设计原创的电路结构。相应的设计流程分为以下四个步骤:

1)系统级,指出电路的特性;

2)行为层,由对电路的算法描述组成;

3)寄存器传输级(RTL),按组成电路结构的组件进行描述;

4)物理层,考虑到实际目标硬件的特征形成描述。

在每一个抽象层次,未知的集成电路都是依靠HDL语言来描述的,如行为VHDL或综合VHDL。最后将准确还原最终电路的 *** 作符和变量。

为了仿真和验证数字电路的功能,需要写入和执行各种测试文件。此外,由于各种模拟HDLs的出现,如Spectre HDL、VHDL - A和的VHDL - AMS,也可以在模拟每个抽象层次电路功能的同时考虑到其实际的环境。另一个可行的方法是在整个开发过程中使用唯一的描述语言。这将在下一篇博文中进行详细讲述。图3描述了自上而下的分层设计方法和HDL开发环境。

最近,FPGA的厂商已经设计出套件软件,使其既能进行模拟仿真,也可自动综合成设计代码。例如,Xilinx的ISE设计套件中的system generator即可完成此功能。(可以参考)

仿真结果是“准确的位和时序周期”,这意味着在一个完全匹配Simulink仿真环境里面可以看到硬件执行的结果。这种做法提供了一个基于FPGA的快速原型设计平台。在这之前,自动代码生成的概念已被成功应用在DSP处理器中(例如Maltab的Target Support Package中的Texas Instruments模块就可以产生C2000上用于整个电机控制的复杂的多闭环控制算法,并集成AD转换,PWM产生,脉冲编码单元、捕获单元、串行接口、CAN等各种接口)。毫无疑问,这种解决方案在不久的将来会越来越多地应用在新的控制算法评估中。然而到目前为止,这种方法仍仅限于不含复杂时序的设计的中。事实上,因为由此产生的设计硬件结构不是面积最优化,故在实际工业上这是不被广泛接受的。

最后,附上IEEE中所有关于HDL、ASIC设计的标准(参考?queryText=(HDL)&refinements=4294965399&openedRefinements=*&matchBoolean=true&rowsPerPage=100&searchField=Search All Text&sortType=asc_PublicaTIon Year&pageNumber=1&resultAcTIon=SORT)。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)