JESD204B是最新的12.5 Gb/s高速、高分辨率数据转换器串行接口标准。转换器制造商的相关产品已进入市场,并且支持JESD204B标准的产品预计会在不久的将来大量面世。JESD204B接口的主要价值在于,它能够可靠地增加转换器和逻辑器件(比如FPGA或ASIC)之间的数据传输带宽。

与任何新接口一样,JESD204B同样带来了新的挑战。对于系统开发人员而言,他们面临的挑战是如何从PCB设计的角度实现JESD204B最佳部署,以及出现问题后如何进行系统调试。对于元件制造商而言,他们面临的挑战包括测试全新的JESD204B器件。测试不仅可以保证器件在相对理想的环境下符合规范,还能确保JESD204B器件在最终系统环境下的正常工作。

本文讨论JESD204B规范,回顾验证JESD204B器件所需的测试,并罗列重现最终系统环境的方法。

JESD204B—数据转换器的自然演进

从音频和音乐到测试仪器仪表,很多应用都要用到数据转换器(数模转换器和模数转换器)。数据转换器的产品处于不断演进中。随着位深和采样速率的增加,数据输入与输出也变得越来越困难。十年或二十年前,高速转换器的采样速率不超过100 MSPS,因此使用TTL或CMOS并行数据总线就足够了。例如,可将集成12个数据专用引脚的12位转换器设置为相对于时钟而言具有适当的建立与保持时间。

JEDEC标准组织发布了两种版本的JESD204高速串行数字接口规范。JESD204 2006规范是第一个版本,该版本为数据转换器带来了SerDes高速串行接口的优势,最高额定速度为3.125 Gbps。该版本于2008年发布了修订版(JESD204A 2008规范),并加入了重要的增强特性,包括支持多条数据通道和通道同步。JESD204B是该规范的第二个版本,由国际JEDEC JC-16任务组(项目:150.01)开发,该任务组由25家公司的约65名成员组成。它提供一系列重大增强特性,包括更高的最大通道速率、支持通过接口的确定性延迟,以及支持谐波帧时钟。

缺少官方兼容性测试规范

与其他很多高速串行接口标准不同,JESD204B标准不含官方兼容性测试规范。测试规范的价值极高,因为它列出了确保兼容性所必须执行的测试,以及测试步骤。让不同制造商使用统一的步骤有助于确保对规范取得共识,并消除假设性差异。但缺少官方的兼容性测试规范并不意味着缺少一切。开发一组测试与步骤所需的一切信息均已包含在JESD204B规范,以及相应规范中。各芯片制造商和系统开发商需收集这些信息。

物理层测试

物理层(或称PHY)测试与各数据通道驱动器和接收器电路有关:换言之,它是链路的模拟测试。它们不包括数字功能性测试或程序性测试。开发完整的PHY测试列表时,可从OIF-CEI-02.0规范第1.7节中获取SerDes PHY测试的推荐列表。JESD204B规范严格遵循这些建议,但作了部分修改。例如,JESD204B未将随机抖动指定为独立测试项目,而是将其包含在总抖动中。另外,JESD204B指定JSPAT、JTSPAT和经过修改的RPAT作为建议测试图案,而OIF-CEI-02.0规范则采用PRBS31图案。

除了所需的PHY测试外,还可执行额外的PHY测试——一些OIF-CEI-02.0规范或者JESD204B规范的PHY部分未列出的测试。比如,可以参考其他SerDes兼容性测试规范,并采用诸如对内偏斜(针对Tx)和对内偏斜容差(针对Rx)等测试。提到这些并不是为了建议将这些测试纳入JESD204B规范中,因为确保JESD204B兼容性不需额外的PHY测试;提到这些内容的目的是为了提醒人们:如果某个PHY测试失败,可以使用其他PHY测试来帮助了解失败的原因。

确定测试列表后,可从JESD204B规范获得关于这些测试的限制。只需记住存在三类限制:LV-OIF-11G-SR、LV-OIF-6G-SR和LV-OIF-SxI5。某个特定的JESD204B器件可支持多种限制。这种情况下,应测试元件支持的全部限制。

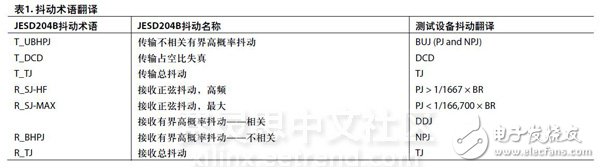

JESD204B PHY测试可能产生的一种混淆与抖动术语有关。JESD204B和OIFCEI-02.0规范使用不同的术语,因而不同测试设备供应商使用的术语也有所不同。典型抖动图如图1所示。测试设备生产商的术语依据工业标准双Dirac抖动模型。这种术语上的不同可能会影响测试步骤,而抖动又是非常棘手的问题。表1显示的是我们翻译的抖动术语(JESD204B规范使用的抖动术语和测试设备供应商有所不同)。

图1. 典型抖动图,包括识别有界不相关抖动(BUJ)

JESD204B PHY测试的另一处可能混淆的地方是数据速率超过11.1 Gbps的眼罩。JESD204B规格中,对于高于11.1 Gbps的数据速率,应使用11.1 Gbps归一化位时间。因此,如果工作速率为12.5 Gbps(位周期为80 ps),则应使用11.1 Gbps(90.9 ps)位周期。这里的问题是,眼罩可以始于UI的边缘,也可以始于UI中心,而JESD204B并未明确定义其起始参照点。如果参照点是UI中心,则在12.5 Gbps时眼罩比一般情况下要大,因而Tx更不容易通过,但便于Rx工作。如果参照点是UI边缘,则在12.5 Gbps时眼罩比一般情况下要小,因而Tx更容易通过,但不利于Rx工作。在这个问题得到解决以前,建议对两个眼罩选项分别进行测试,以保证兼容性。

时序测试

列出JESD204B的完整时序测试列表是非常困难的。在整个规范中,至少定义了十几种时序图,而且无法很快确定Tx、通道或Rx各自对应的时序。此外,某些时序仅适用于特定的子类(0、1或2)。如果只是简单地将时序规格整合到一张表格内,那么官方兼容性测试规范将起到非常大的作用。只要花一些时间系统地了解这些时序规范,就不会产生混淆。

对于系统开发人员来说,有关时序的一个好消息是,为JESD204B元件设定时序比从规格中直接获取相关信息更容易了。对于子类0和2来说,只需指定器件的时钟到SYNC~时序。对于子类1而言,只需指定器件的时钟到SYSREF时序。

协议测试

对于PHY测试,没有官方的JESD204B协议测试列表。因此,用户需自行浏览规范内容,并编写待测功能列表。本节罗列了大量推荐协议测试,并给出简要说明。

有一类协议测试专门测试序列。对于PHY测试,JESD204B发送器必须要能够输出JSPAT并修改RPAT图案。从协议角度来看,需验证这些图案的正确性。JESD204B接收器以及JTSPAT图案同样如此。或者,如果支持PRBS图案,那么也需对其进行验证。下一步是短传输层和长传输层图案。这些内容可以证明链路通过传输层后工作正常,以帮助系统开发人员进行系统调试。就元件制造商而言,需针对器件支持的每一种工作模式验证这些传输层图案;考虑到链路配置变量的数目,这将会产生大量的不同情况。

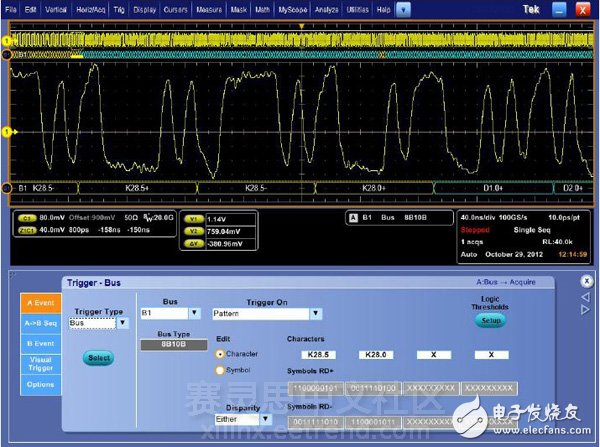

有关协议测试带来的一个问题是如何在12.5 Gbps下完成。一种建议的解决方案是使用带串行数据解码器的高速示波器。现在很多高端示波器都配备了专用触发芯片,触发8b/10b数据,以支持JESD204B。图3显示JESD204B数据通道在6 Gb/s下的串行解码,位置是初始通道对齐序列(ILAS)的起点。

图2. 在6 Gbps下对JESD204B数据通道进行串行解码,并显示ILAS序列的起始

另一组协议测试可围绕ILAS构建。ILAS作为整体而言非常复杂,因此将其分配到各独立的元件能让协议测试更有意义。下列测试示例可用于发送器的测量,验证其工作情况。多帧长度正确吗?是不是每个多帧都以/R/控制码开头,以/A/控制码结尾?/Q/控制码是否位于正确的位置?链路配置数据及其位置是否正确? ILAS含有数据,是真的吗?ILAS持续几个多帧?是否所有通道上的ILAS都相同?显然,围绕ILAS序列展开的协议测试具有很大的潜力。

JESD204B没有太多握手,但如果有的话就能被测试。取决于子类,可执行一系列测试。由于SYNC~信号可用作初始握手、错误报告以及链路再初始化,Tx和Rx元件是否正确执行相应的功能? Rx置位SYNC~是否始于正确的时间,且持续正确的时间? Tx是否根据SYNC~置位的持续时间而作出正确的反应? 由于通过链路发送的数据同样参与了握手(比如ILAS),其内容是否正确,并对应于SYNC~时序?

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)