低温漂低功耗的带隙基准源技术设计

摘 要:设计一种低温漂低功耗的带隙基准结构,在传统带隙基准核心电路结构上增加一对PNP管,两个双极型晶体管叠加的结构减小了运放的失调电压对输出电压的影响,降低了基准电压的温度失调系数。电路设计与仿真基于CSMC 0.5 μm CMOS工艺,经流片,测得室温下带隙基准输出电压为1.326 65 V,在-40~+85 ℃范围内的温度系数为2.563 ppm/℃;?在3.3 V电源电压下,整个电路的功耗仅为2.81 μW;在2~4 V之间的电源调整率为206.95 ppm。

关键词:带隙基准;低温漂;低功耗;CMOS

便携式电子产品在市场上占有越来越大的份额,对低电压、低功耗的基准电压源的需求量大大增加,也导致带隙基准的设计要求有了较大的提高。带隙基准广泛应用于数/模转换、模/数转换、存储器以及开关电源等数模混合电路中。基准源的稳定性对整个系统的内部电源的产生,输出电压的调整等都具有直接且至关重要的影响。基准电压必须能够克服制造工艺的偏差,系统内部电源电压在工作范围内的变化以及外界温度的影响。

由文献可知传统的一阶补偿通常可以得到10 ppm/℃左右的温度系数,而新发展的比较成熟的补偿技术,包括二阶温度补偿,分段线性补偿,指数温度补偿等其他的补偿方法,文献中所提及的电路的结构均比较复杂,或受到比较多的工艺的限制,或运用BiCMOS工艺,其制造成本比较高。在此设计一种以共源共栅电流镜为负载的低温漂高电源抑制比CMOS带隙基准电压源,利用新型核心电路和NMOS为输入管的套筒式共源共栅运算放大器使得带隙基准的输出温度系数远小于传统带隙基准的温度系数。

1 曲率补偿的带隙基准

1.1 VBE的温度特性

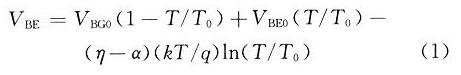

由文献可知,双极型晶体管的VBE的温度曲线不是简单地随温度做线性变化的,其温度特性为:

其中:VBG0为由零度推导出的PN结外接电压;T0为参考温度,T为绝对温度;VBE0是双极晶体管在温度为T0时的发射结电压;η为与温度无关,但与工艺有关的一个参数;α的值与集电极电流Ic的温度特性有关(I0与温度成正比即PTAT电流时α=1;当I0是与温度无关的电流时,α=0)。

式(1)中与温度相关的非线性项作泰勒展开可得:

其中:α0,α1...αn为常数项,传统的带系基准电路工作时只将VBE和温度有关的非线性项的一次项消除,输出值仍与温度的高阶项呈现非线性的相关性。要进一步的降低输出的温度相关性,就要使用新方法对VBE的非线性温度系数进行补偿。

1.2 带隙基准原理

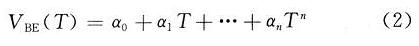

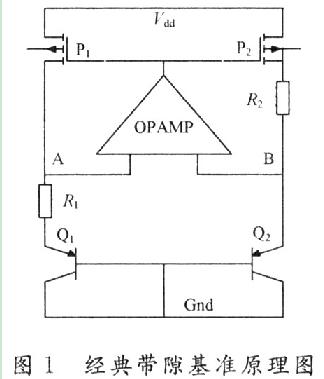

传统带系基准的电路如图1所示,其主要由衬底PNP、电阻和运放构成。利用具有负温度特性的双极型晶体管的VBE与具有正温度特性的热电压vt,在适当的系数下将两者叠加,从而得到与温度无关的基准电压。在T0处,推导式(1)与温度的关系:

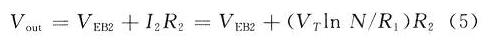

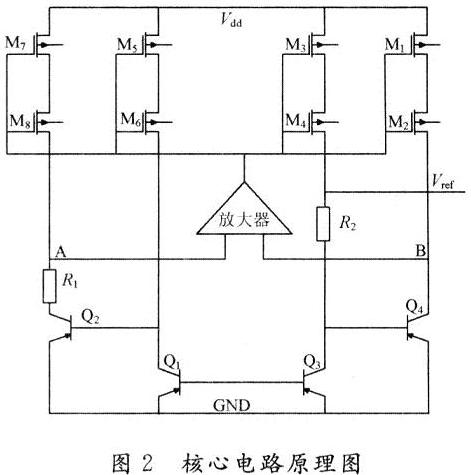

处于深度负反馈的运放强制A,B点电压近似相等,假设电阻R1,R2上流过的电流分别为I1和I2,而N为Q1,Q2发射极面积之比,因此:

宽长比相同的PMOS管P1,P2使两条支路的电流近似相等,且具有相同温度特性,就可以得到以下输出参考电压:

上式对在T0处温度求导可得:

联合上式和式(3)可以看出,只要选择合适的电阻R1,R2值和数值N就可以得到一个温度系数接近零的输出电压。

带隙基准在设计中非常注重运算放大器这个环节。首先运算放大器的输入匹配要求比较高,核心电路中PTAT电流的产生对后面有决定性的影响,如果可以设计一种高匹配的PTAT电流源,就可以保证运算放大器的输入端的匹配,使基准电压的产生有了基本保障。其次运算放大器有失调电压,失调电压也将被运算放大器放大,运放增益越大则被放大的噪声越大。使用新的PTAT电流产生方法,使得能在带隙基准中使用较低增益的运算放大器,就可以进一步减小输出电压中包含的运算失调电压的影响。

2 新型带系基准的设计与分析

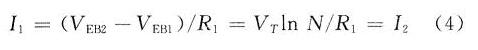

在温度300 kΩ 时,VBE的温度系数约为一2.2 mV/℃,VT的温度系数约为O.86 mV/℃。这里所提出的核心电路如图2所示,使用双极型晶体管构成电路的核心部分,实现VBE和VT的线性叠加,得到温度系数近似为零的输出电压。

2.1 核心电路

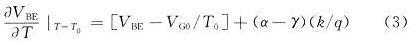

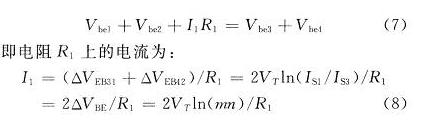

图2中Q1和Q2,Q3和Q4的发射结面积相同,根据设计需要,取Q1和Q2的发射结面积为Q3和Q4的发射结面积的46倍。假设双极型晶体管基极电流为零,且运放的增益足够大,则A点和B点的电压被迫相等:

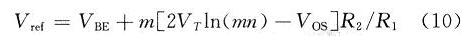

其中:m为2条支路上的电流的比值;n为Q1和Q2的发射结面积之比。该电流是与绝对温度成正比的PTAT电流,且与电源电压无关。Vref的值为:

图2采用2个双极型晶体管叠加的结构,主要目的是减小运放失调电压对输出电压的影响。假设运放的失调电压为VOS,得到以下输出电压:

由上式可得,要减小运放的失调电压的影响,可以增大括号中的第一项,也就是增大m或竹的值,取Q,和Q2的发射结面积为Q3和Q4的发射结面积的46倍就是为了减小失调电压对输出的影响,使用比较大的n值;其次,两个相叠的双极型晶体管使运算放大器的两个输入电压中均含有两个叠加的VBE,减小核心电路中对运算放大器的增益的需求,使得使用的运算放大器的增益小于传统带隙基准中的运算放大器的增益,从而使输出中减小了运放失调电压对输出电压的影响。两种方法使该电路输出的基准电压有比使用传统核心电路更低的温度系数。

此电路的缺点是比普通带隙基准多消耗1个电压余度,两个叠加的双极型晶体管需要多消耗1个VBE,大约是0.7 V的电压。电源电压Vdd,至少需要2VBE+VDS1+VDS2,其中VDS1和VDS2分别为M1和M2的源漏电压,共计3 V左右。在低电源电压中应用这种结构对共源共栅电流镜的输出电压摆幅即所消耗的电压余度的要求比较高。

2.2 运算放大器的设计

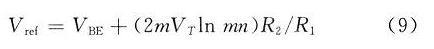

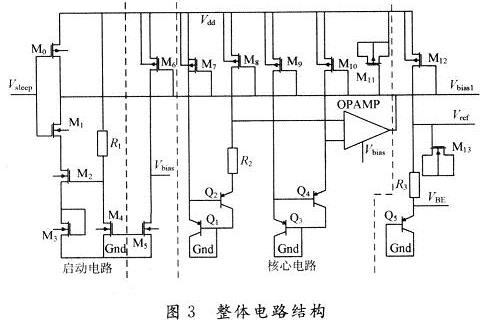

要使带隙基准有高的电源抑制比,电路中使用的运放开环增益和电源抑制比就必须足够大。计算得运放增益大约60 dB,使用了套筒式共源共栅结构,以NMOS管作为输入管,两对PMOS管作为负载管。套筒式结构简单,功耗和消耗的电压余度和都相对要更小,比较适合设计中低功耗的需求,并且可以解决核心电路中叠加的双极型晶体管多消耗的一个电压余度。图3是带隙基准整体结构图,启动电路在核心结构正常工作后自动关断,由图可知运算放大器所需要的偏置电流由带隙基准产生。

3 测试结果分析

基于CSMCO.5μm DPTM CMOS工艺对版图进行设计、流片。电路概貌图如图4所示。

图5是在3.3 V的电源电压下,一40~+85℃的工作温度范围内带隙基准的温度特性曲线;表1是将电源电压的设定范围为2~4 V,对带隙基准电路的输出电压进行测试,得到的电源电压特性。

图5 3.3 V电源电压下,温度为一40~+85℃时的输出电压与工作温度曲线图5表示的是基准电压源的温度特性曲线,测试结果表明此电压源在工作温度范围内,温度系数为2.563 ppm/℃。

表1是电源电压特性分布,在室温下,电源电压在2~4 V间变化时的输出电压,由表1可知,此电压源在电源电压为2 V时就可以正常工作。基准电压源在2~4 V间的输出差值为413.9μV,即电源调整率为206.95 ppm。

蒙特卡罗分析是用于衡量器件特性值对电路性能影响的一种测试分析方法。在每个蒙特卡罗分析中,器件的特征值被当作潜在影响测试结果的因素并进行分类,由于测试是随机选取样本,各个特征值也将是随机。在一个完整的测试结束后,可以得到1个或多个结果。每一项性质将得到一系列可被统计学统计的结果。对带隙基准而言,主要特征值包括制造中的掺杂浓度的分布,内部电源电压值的偏差和外界的温度变化。

分析测试结果的方法是将它们归纳在不同范围中,每个范围表示在所有结果中占有的比例。将这些范围用柱状图表示出来,每部分柱状图都由其高度表示在总体中占有的数量。

图6是在室温下选取80个芯片并对其带隙基准电路输出电压测试。由图可以看出,输出电压有95%以上都分布在设计的输出电压周围,在实际应用中不需要trim就可以得到合适的输出电压。

4 结 语

这里设计了一种具有低温漂低功耗且不需要trim的基准电压源,利用低压共源共栅电流镜来减小输出电压对电源电压的依赖。测试结果表示:电路在2 V电源电压下就可以正常工作,输出基准电压为1.326 65 V;在-40~+85℃之间的温度系数为2.563 ppm/0C;电路在3.3 V电源电压下,功耗仅为2.81 μW,可以广泛应用在移动电子设备中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)