电子镇流器的供电方式为半桥输出接稳压管给芯片供电,其输出电压为高压正弦波(50~100 kHz),加之芯片内数字部分的干扰,这就给芯片的电源带来较大的干扰。因此对芯片内基准的中频PSR(Power Supply RejecTIon,电源抑制)有较大要求。本文从此角度在Brokaw带隙基准的基础上进行改进,采用LDO与基准的级联设计来增加其PSR。

1 电路结构

1.1 基准核心

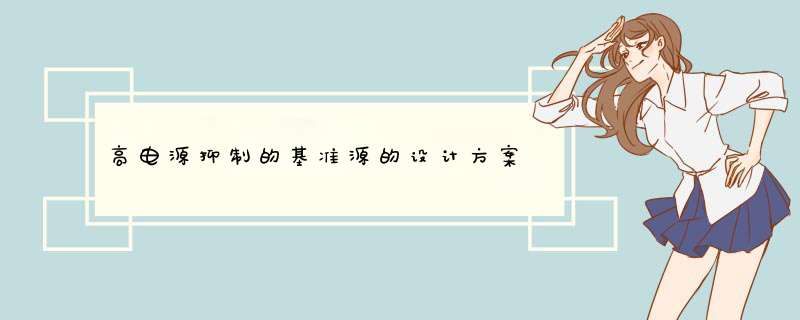

目前的基准核心可以有多种实现方案:混合电阻,Buck voltage transfer cell,但是修调复杂,不宜工业化。本设计采用Brokaw基准核心,其较易实现高压基准输出,并且其温漂、PSR及启动特性均较好。本文采用的改进的Brokaw基准核心的结构如图1所示。

对此核心的分析:

三极管的输出电流公式:

其中I是三极管射极电流,Is与射极面积成正比,n为一常数,取1。这里,取VQC2:VQC1=8:1,因此Is2=8xIs1,又I1=I2,分别代入(1)并相除,整理得:

其中Vbe1是负温度系数,Vt是正温度系数,RC2与RC1是同类电阻,温度系数相抵消,选择合理的RC2/RC1,就可以得到一阶补偿为0的基准电压,可以很好的满足本芯片的要求。

在电流镜的选取上,采用威尔逊电流镜,精度高,不需外加偏置电路,因此电源抑制比较高。输出管采用mos管,对VQC5、VQC1支路电路影响小。通过增加MC1,使VQC2和VQC1的集电极电位相近,减小误差。

产生的Vref为4.75 V,在放大电压的同时,PSR、温漂均放大了4倍,即PSR升高了12 dB(在随后的仿真波形中可以看到)。

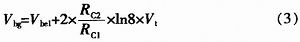

1.2 LDO

LDO在低频时的PSR主要取决于运放的增益,为此选择折叠共源共栅电路。此LDO电路基于文献中的电路修改,如图2所示,并采用PSR高的偏置生成电路。

1. 3 启动电路

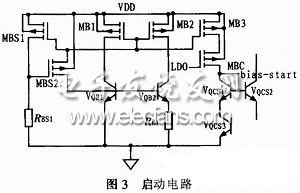

Brokaw核心本身存在0状态,VQC5基极为高电平,VQC2、VQC1基极为低电平,因此引入如图3的启动电路。

图3中右下角即为启动电路。对于常规Brokaw基准,当VQC2基极电压低于启动电压时,VQCS2将VQC5基极电压拉低VQC2基极电压拉高,使电路启动,所以VQCS2仅需很小的基极电流就可以使电路启动。

但是,由于本设计采用LDO供电,而LDO的参考电压是bg,存在死循环,即bg低,则LDO低,所以基准核心的VQC5无法给VQCS2提供电流,也就无法提高VQC2的电压即bg,因此需要外界提供大电流bias-start,使得当LDO无法启动基准核心时,此电流可以足够大,在RC4上产生的压降使bg达到足够大,继而LDO达到使基准核心启动所需的最低电压,从而使电路进入自动修正状态,最终使bg和ref达到指定电压。

这样虽然能启动,但是,正常工作时,此大启动电流bias-start将通过VQCS1和VQCS3流向地,增加了系统的负担。因此,在电流输出管MB3下加入控制管MBC,并使得在正常工作时,LDO的高电压足以使MBC关断,从而降低启动电路的损耗。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)