摘要

锁相环(PLL)是现代通信系统的基本构建模块PLLs通常用在无线电接收机或发射机中,主要提供"本振"(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。由于每一代PLL的噪声性能都在改善,因此电源噪声的影响变得越来越明显,某些情况下甚至可限制噪声性能。

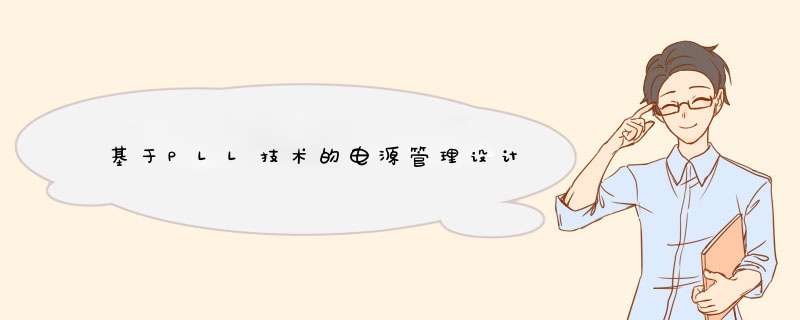

本文讨论图1所示的基本PLL方案,并考察每个构建模块的电源管理要求。

图1.显示各种电源管理要求的基本锁相环

PLL中,反馈控制环路驱动电压控制振荡器(VCO),使振荡器频率(或相位)精确跟踪所施加基准频率的倍数。许多优秀的参考文献 (例如Best的锁相环1),解释了PLL的数学分析;ADI的ADIsimPLL?等仿真工具则对了解环路传递函数和计算很有帮助。下面让我们依次考察一下PLL构建模块。

VCO和VCO推压

电压控制振荡器将来自鉴相器的误差电压转换成输出频率。器件"增益"定义为KVCO,通常以MHz/V表示。电压控制可变电容二极管(变容二极管) 常用于调节VCO内的频率。VCO的增益通常足以提供充分的频率覆盖范围,但仍不足以降低相位噪声,因为任何变容二极管噪声都会被放大KVCO倍,进而增加输出相位噪声。

多频段集成VCO的出现,例如用于频率合成器ADF4350的集成VCO,可避免在KVCO与频率覆盖范围间进行取舍,使PLL设计人员可以使用包含数个中等增益VCO的IC以及智能频段切换程序,根据已编程的输出频率选择适当的频段。这种频段分割提供了宽广的总体范围和较低噪声。

除了需要从输入电压变化转换至输出频率变化(KVCO)外,电源波动也会给输出频率变化带来干扰成分。VCO对电源波动的灵敏度定义为VCO 推压(Kpushing),通常是所需KVCO.的一小部分。例如,Kpushing通常是KVCO的5%至20%.因此,对于高增益VCO,推压效应增大,VCO电源的噪声贡献就更加举足轻重。

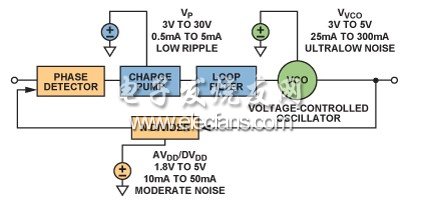

VCO推压的测量方法如下:向VTUNE引脚施加直流调谐电压,改变电源电压并测量频率变化。推压系数是频率变化与电压变化之比,如表1所示,使用的是ADF4350 PLL.

表1. ADF4350 VCO推压测

参考文献2中提到了另一种方法:将低频方波直流耦合至电源内,同时观察VCO频谱任一侧上的频移键控 (FSK)调制峰值(图2)。峰值间频率偏差除以方波幅度,便得出VCO推压系数。该测量方法比静态直流测试更精确,因为消除了与直流输入电压变化相关的任何热效应。图2显示ADF4350 VCO输出在3.3 GHz、对标称3.3 V电源施加10 kHz、0.6 V p-p方波时的频谱分析仪曲线图。对于1.62 MHz/0.6 V或2.7 MHz/V的推压系数,最终偏差为3326.51 MHz – 3324.89 MHz = 1.62 MHz.该结果可与表1中的静态测量 2.3 MHz/V比较。

图2.ADF4350 VCO通过10kHz、0.6v p-p方波响应

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)