用于测试3D IC的解决方案目前已面世,而且会越来越成熟。在2015年的国际测试与失效分析研讨会(ISTFA)上,笔者发表了题为《三维数字测试有何新进展?》(What is New in 3D, Digital TesTIng?)的演讲,本文将总结此次演讲的要点。笔者在演讲中探讨了测试标准和测试挑战,其中包括良品裸晶(known-good-die;KGD)和测试堆栈芯片。

3D IC测试的两个主要目标是提高预封装测试质量,以及在堆栈芯片之间建立新的测试。当然,对于二维(2D)芯片(KGD)的高质量测试是测试三维(3D)堆栈的基本前提条件。业界如今已能有效掌握与理解这些问题,而且也存在良好的解决方案。有几种解决方案可分别用于测试堆栈在逻辑模块上的内存和堆栈在内存上的内存。然而,逻辑模块与逻辑模块(logic-on-logic)堆栈的3D测试仍然处于起步阶段。

为了满足一系列的3D测试需求,业界一直在积极努力完成或更新多种现有的测试标准,包括:

· IEEE 1149.1 (JTAG),广为人知的测试存取标准

· IEEE 1687 (IJTAG),较新的IP访问方法

· IEEE P1838,针对多个芯片之间的3D互 *** 作性以及与其他标准连接而提出的标准

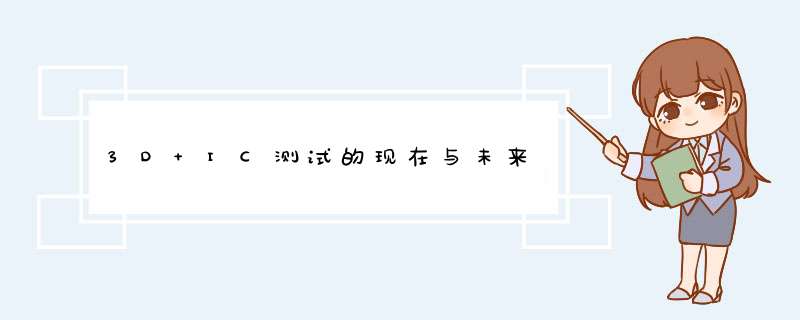

3D对芯片级测试质量意味着什么?在进行3D测试之前,晶圆首先要经历晶圆测试;有些芯片可通过测试,另一些则否。通过测试的裸晶继续进行封装,然后进行封装测试,在这些环节还会发现更多(在上次测试时未发现的)不合格件(如图1)。

图1:传统晶圆和封装测试的比较

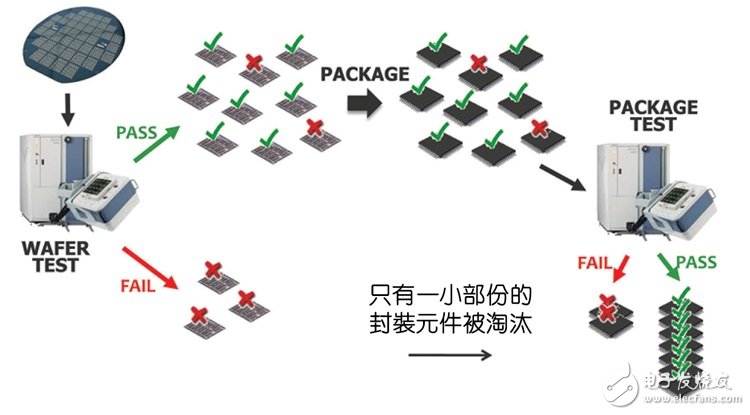

就测试方案本身来说很寻常。然而,一旦开始将多个裸晶封装在一起,那些先前从晶圆级测试中「逃脱」的少量裸晶会让你丢弃更多的封装组件(图2)。

图2:3D堆栈IC的晶圆与封装测试比较

这就会带来很大的问题。笔者做了一些计算:如果裸晶缺陷覆盖率是95%,则10层芯片堆栈的最终封装良率将会是60%。显然地,如果5%的逃脱率导致40%的最终产品被丢弃,这并不是我们希望看到的。这里的关键是3D封装需要非常高质量的晶圆级测试,以便只有「良品裸晶」被封装在一起。

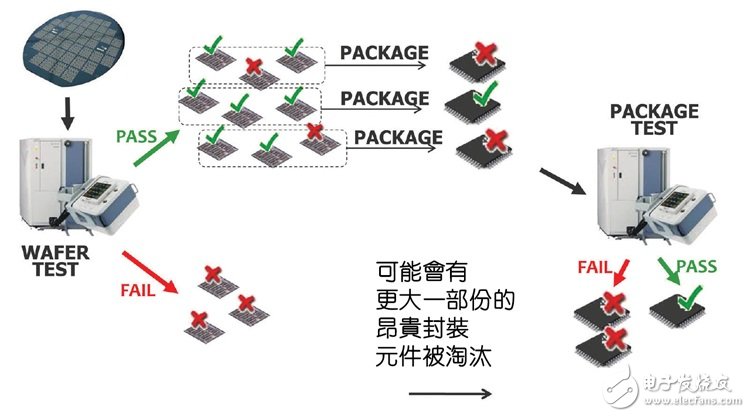

除了满足高质量的良品裸晶要求之外,3D测试还需要已知合格的中介层、部份堆栈测试、硅穿孔 (TSV)和封装测试。单独使用传统「自动测试模式产生」(ATPG)的途径已成为过去。嵌入式测试压缩和逻辑内建自测试(BIST)的组合提供最好的性价比(图3)。

图3:嵌入式测试压缩和逻辑内建自测试组合的优点

逻辑内建自测试组件使系统自我测试成为可能,这对于汽车或医疗应用的IC尤为重要。添加单元内(cell-internal)和非传统失效模型(fault models)则能够使设计中数字逻辑组件的测试质量达到可接受的程度。当然,你还需要测试嵌入式IP、I/O以及TSV。为了存取和测试嵌入式IP,IEEE 1687 IJTAG 提供了用于整合异质IP的IP和测试模式重用(pattern reuse)方法。甚至有工具已经可以自动化许多设计和测试任务来支持IJTAG方法。

对于I/O和TSV,因为无法保证与ATE的电气接触,测试必须在「非接触」形式下进行。这是一个有待研究的领域;其中一种有趣的做法是使用边界扫描途径,为部份封装的组件进行晶圆级测试,以及封装内芯片之间的互连测试。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)