1、clk中为什么用posedge而不用negedge?

(1)、一般情况下,系统中统一用posedge避免用negedge,降低设计的复杂度,可减少出错。

(2)、在modelsim仿真中,时钟是很严格的,但是在真实的晶振所产生的clock却是不严格的,比如高电平和低电平的时间跨度就不一样,甚至非周期性的微小波动。如果只是用posedge,则整个系统的节拍都按照clock上升沿对齐,如果用到了negedge,则系统的节拍就没有统一到一个点上。上升沿到上升沿肯定是一个时钟周期,但是上升沿到下降沿却很可能不是半个周期。

(3)、FPGA特有的东西:GLOBAL clk。FPGA内部有专门的时钟线,和一般的逻辑门走法不一样,目的是为了保证整个FPGA内部时钟尽可能的偏差小。

2、BANK划分与供电策略

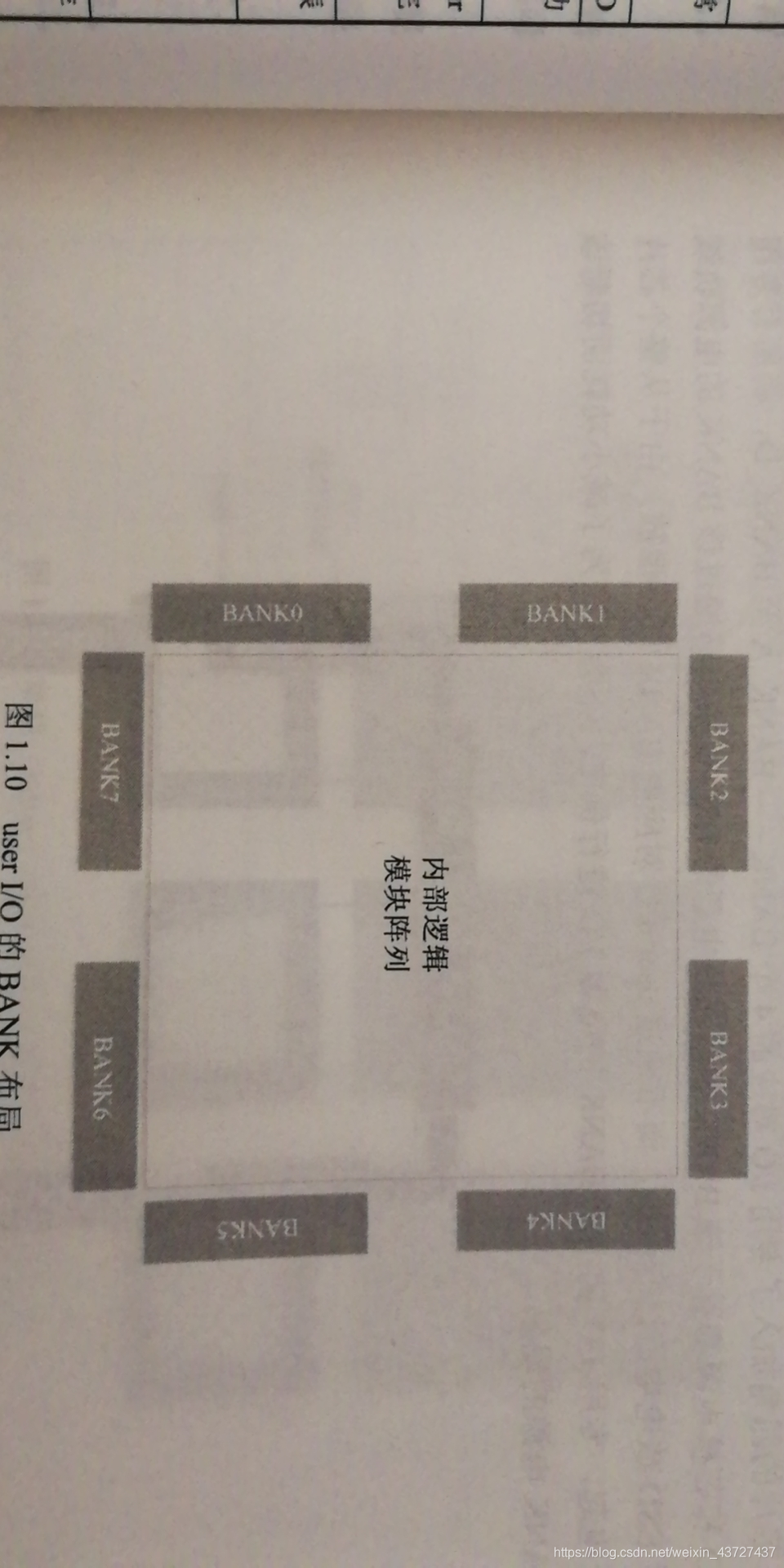

FPGA内I/O的排布是通过BANK划分来实现的,若干user I/O与电源I/O被划分为一个BANK。如下图,整个芯片的user I/O被分成8个BANK。BANK与BANK之间是相互独立的。每个BANK的user I/O可由不同电平的电源供电而不会相互影响。不同BANK的user I/O可以配置为不同的I/O标准和电平标准,提高了user I/O使用的灵活性。

由同一个电源供电的多个user I/O同时跳变时,会带来相当大的瞬时动态电流。由于PAD和封装引起的电感,这个电流可能会在电源轨线上带来压降,严重时会因逻辑电平降低而引起翻转,使电路工作失效。

采用划分BANK的方法对user I/O进行排布,可以有效改善这个问题。将FPGA中所有的user I/O划分为多个BANK分别进行独立的供电,用户在编程时将使用到的user I/O配置于不同的I/O BANK,可以控制每个BANK内同时翻转的user I/O的数量,降低瞬时的动态电流,也可以避免触地反d现象的出现。对于没有使用到的BANK,还可以关闭该BANK的电源,能够有效降低功耗。

FPGA中的user I/O一般通过划分BANK的方式独立进行供电,为保证器件在输出电流驱动片外负载的情况下能够正常工作,并保证ESD放电现象发生时,电源轨线不会因瞬间的高热而熔断烧毁,I/O的电源轨线必须满足一定的宽度,且留有足够金属通孔(VLA)数量。在设计前期,由BANK内user I/O的数量、I/O最大驱动电流以及BANK内电源PAD数量对BANK内电源轨线上通过最大电流进行预估,根据Foundry提供的金属电流密度参数,设计合理的电源轨线宽度。

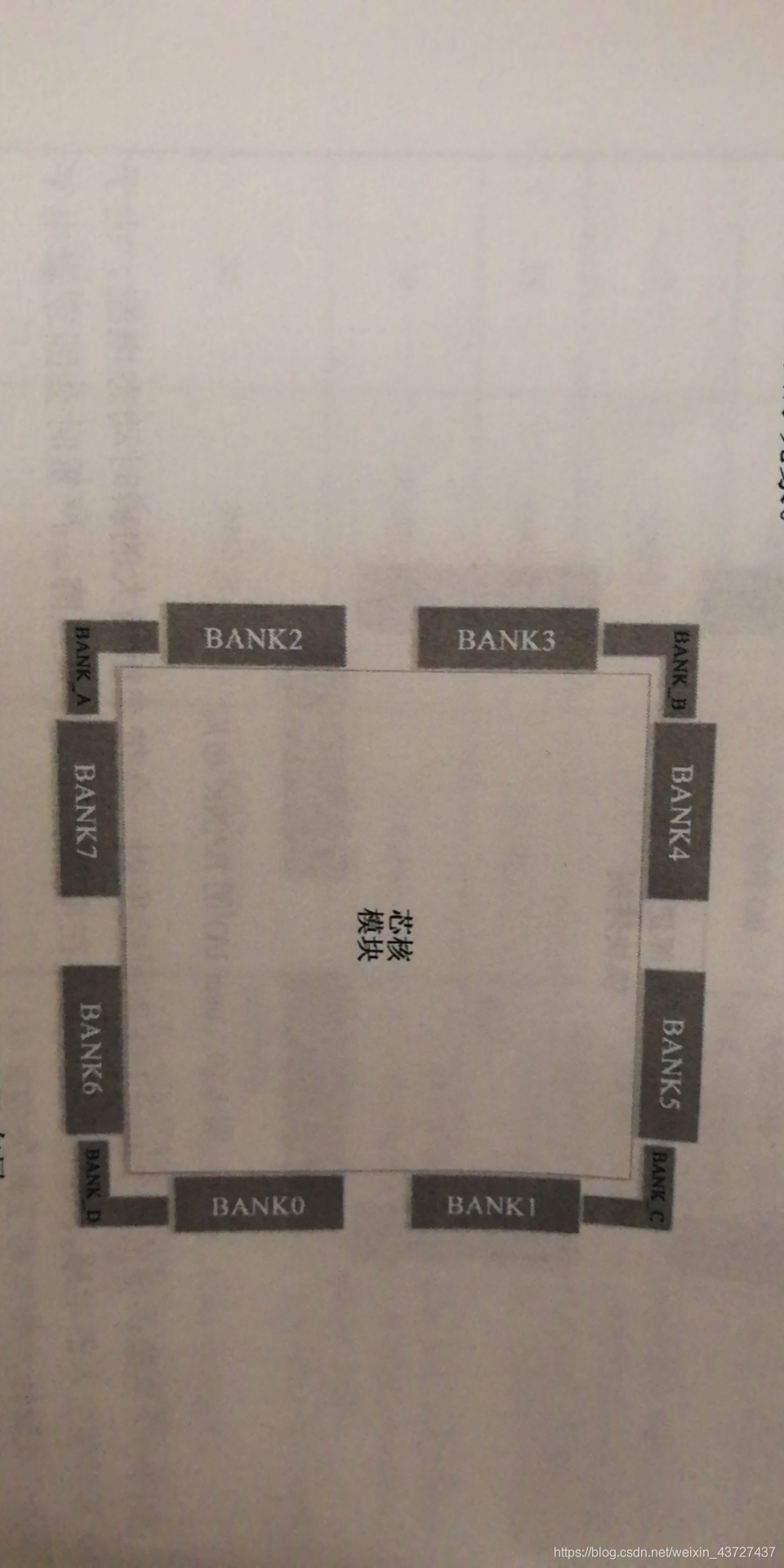

在FPGA中,一般有多个专用I/O的供电和特点,对整个FPGA芯片的BANK布局进行改造,保持user I/O的8个独立BANK不变,在芯片的四角加入了专用I/O对应的4个BANK----BANKA-BANKD,将所有专用IO和芯核,电源都置于该BANK中,芯核电源的ESD保护电路通过该BANK的电源轨线对ESD放电电流进行泄放,而不通过user I/O对应的BANK进行泄放。由于从整个芯片上电起,专用I/O就由该BANK的电源I/O进行供电,不会存在为了减小功耗而切断该BANK电源的现象。

3、为什么verilog HDL设计中一定要用同步而不能用异步时序逻辑?

同步时序逻辑是指状态的寄存器组的值只可能在唯一确定的触发条件时刻改变。只能由时钟的正条边沿或负跳变沿触发的状态机就是一例。always@(posedge clock)就是一个同步时序逻辑的触发条件,表示由该always控制begin end块中寄存器变量重新赋值的情形只可能是在clock正条边沿发生。

而异步时序逻辑是指触发条件由多个控制因素组成,任何一个因素的跳变都可以引起触发。记录状态的寄存器组其是在输入端不是都连接在同一个时钟信号上。例如用一个触发器的输出连接到另一个触发器的时钟端去触发就是异步时序逻辑。

用Verilog HDL设计的可综合模块,必须是避免使用异步时序逻辑,这不但是因为许多综合器不支持异步时序逻辑的综合,而且也因为用异步时序逻辑确实难以控制由组合逻辑和延迟所产生的冒险和竞争。当电路复杂度增加时,异步时序逻辑无法调试。工艺的细微变化也会造成异步时序逻辑电路的失效。因为异步时序逻辑中触发条件很随意,任何时刻都有可能发生,所以记录状态的寄存器组的输出在任何时刻都有可能发生变化。而同步时序逻辑中的触发输入至少可以维持一个时钟后才会发生第二次触发。这是一个非常重要的差别,因为我们利用这一个时钟的时间在下一次触发信号到来前,为电路状态的改变创造一个稳定可靠的条件。

因为我们可以得出结论:同步时序逻辑比异步时序逻辑具有更可靠更简单的逻辑关系。如果我们强行做出规定,用Verilog来设计可综合的状态机必须使用同步时序逻辑,有了这个前提条件,实现自动生成电路结构的综合器有了可能。一碗这样大大减少了综合工具的复杂度。

同步、异步时序逻辑的差异:

在同步逻辑电路中,触发信号是时钟的正跳变沿(或负跳变沿);触发器的输入与输出是经由两个时钟来完成的。第一个时钟的正跳沿(或负跳沿)为输入做准备,在第一个时钟正跳沿(或负跳沿)到来后到第二个时钟正跳沿(负跳沿)到来之前这段时间内,有足够的时间使输入稳定。当第二个时钟正跳沿(负跳沿)到来时刻,由前一个时钟沿创造的条件已经稳定,所以能够使下一个状态正确地输出。

若在同一时钟的正跳沿(负跳沿)下对寄存器组既进行输入又进行输出,很有可能由于门的延迟使输入条件还未确定时,就输出了下一个状态,这种情况会导致逻辑紊乱。

而利用上一个时钟为下一个时钟创造的触发条件是安全可靠的。前提是:确定下一个状态所使用的组合电路的延迟与时钟到各触发器饿的差值必须小于一个时钟周期的宽度。只有满足这一前提才可以避免逻辑紊乱。实际电路中有以下几点可以保证这一条件成立:

(1)、全局时钟时钟网络布线时尽量各分支的时钟一致;

(2)、应平衡树结构,在每一级加入缓冲器,使到达每个触发器时钟端的时钟同步。

通过这些措施基本可以保证时钟的同步,在后仿真时,若逻辑与预期设计的不一样,可降低时钟频率,就有可能消除由时钟过快引起的触发器输入端由延迟和冒险竞争造成的不稳定从而使逻辑正确。

在组合逻辑电路中,多路信号的输入使各信号在同时变化时很容易产生竞争冒险,从而结果难以预料。

4、funcTIon and task

funcTIon的逻辑被综合成了什么?

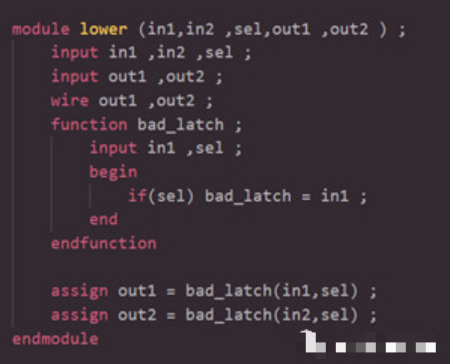

由于funcTIon中没有任何时序结构,funcTIon只能综合出组合逻辑。

每次调用function时,局部变量和返回值都被赋值,否则将导致形成锁存器。例如,以下示例中,if条件语句没有else语句。也就是说,如果sel是false,该function将返回其先前调用的值,就好像结果被锁存住了。

fucntion只用于综合成组合逻辑。但是,fucntion的最终结果可以用作D触发器的输入。

fucntion不应包括延迟(#)或事件控制(@,wait)语句。

fucntion可以调用其他fucntion,但不能调用task。

fucntion在调用时会返回一个值。

虽然在task中可以有@等时序控制结构中,它仅适用于仿真。综合工具会忽略所有task中的时序结构。因此,如果task中存在时序控制结构,可能会存在仿真和综合不匹配的现象。

因此,在可综合verilog中一般只会使用task综合基本的组合逻辑,在testbench中调用带有时序控制结构的task具有较好的通用性。

5、FPGA设计技巧

DSP:实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。换言之,FPGA可以更容易实现多个DSP core功能。在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

SERDES:高速串行接口。将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。有了SERDES模块,FPGA可以很容易将这些高速串行接口集成进来,无需再购买专门的接口芯片。

CPU core:分为2种,软core和硬core。软core是用逻辑代码写的CPU模块,可以在任何资源足够的FPGA中实现,使用非常灵活。而且在大容量的FPGA中还可以集成多个软core,实现多核并行处理。硬core是在特定的FPGA内部做好的CPU core,优点是速度快、性能好,缺点是不够灵活。

FPGA设计技巧(1):时钟树

对于FPGA设计来说,要尽可能的避免异步设计,尽可能的采用同步设计。同步设计的第一个关键是时钟树。时钟树的设计原则如下:

(1)尽可能采用单一时钟

(2)如果有多个时钟域,注意时钟域的划分

(3)跨时钟域的信号一定要做同步处理。对于控制信号,可以采用双采样;对于数据信号,可以采用异步fifo。需要注意的是,异步fifo不是万能的,一个异步fifo也只能解决一定范围内的频差问题。

(4)尽可能使用FPGA内部的PLL、DLL和MMCM,不要自己产生时钟。

(5)对于特殊的IO接口,需要仔细计算Tsu、Tco、Th,并利用PLL、DLL、DDIO、管脚可设置的delay等多种工具来实现。简单对管脚进行Tsu、Tco、Th的约束往往是不行的。

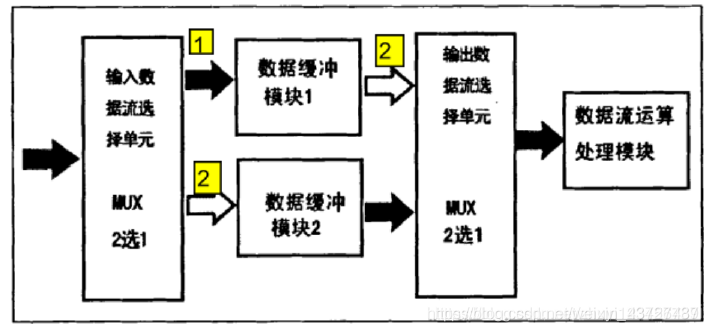

FPGA设计技巧(2):乒乓 *** 作

乒乓 *** 作是FPGA设计中经常用到的设计思想,常用于需要提高数据效率的地方。其主要特点有:

1、 实现数据的无缝缓冲和处理;

2、 可节约缓冲区空间;

3、 可实现低速模块处理高速模块如图所示:

T1时刻,DATA_T1存入buffer 1;

T2时刻,buffer 1已被写满,DATA_T2存入buffer 2, 同时buffer 1将DATA_T1送至运算模块处理;

T3时刻,DATA_T3存入buffer A1,同时buffer 2将DATA_T2送至运算模块处理;

然后重复2、3阶段的 *** 作。

FPGA设计技巧(3):串并转换

串并转化的思想,旨在与提升运算和芯片运行的速度,串行转并行已经成为设计中不可缺少的一种思维。

串转并的设计思想具体是这样的,首先准备好一组寄存器,当来了一位数据的时候,寄存器组左移(右移)一位,然后把发送过来的数据寄存到寄存器组的最低位(最高位),当一组数据完整接收完毕的时候,标志位会变高,表示当前数据可以采样。

module study(clk, rst_n, data, data_out); //端口列表input clk, rst_n; //时钟,复位输入input data; //输入数据output reg [7:0] data_out;reg [3:0] count; reg [7:0] temp;always @ (posedge clk or negedge rst_n) //时序逻辑,异步复位if(!rst_n)

begin

data_out <= 0;

temp <= 0;

count <= 0;

end

else if(count < 8) //计数表示只接8个数据 begin

temp <= {temp[6:0],data}; //移位寄存器 count <= count +1'b1;

end

else

begin

data_out <= temp; //接到后输出 endendmodule

采用计数方法,将并行的数据的总数先表示出来,然后发送一位数据减一,后面的接收的这样表示: data_out <=data[cnt];

module study(clk, rst_n, data, data_out,load,turn); //端口列表input clk, rst_n; //时钟,复位输入input data; //输入数据input load; //并行数据使能信号input turn; //串行数据使能信号output reg [7:0] data_out;reg [7:0] temp;always @ (posedge clk or negedge rst_n) //时序逻辑,异步复位if(!rst_n)

begin

data_out <= 0;

temp <= 0;

end

else if(load)

temp<=data;

else if(turn) //计数表示只接8个数据 temp <= {temp[6:0],temp[7]}; //移位寄存器 else

begin

temp <= temp[7]; //接到后输出 endassign data=temp;endmodule

FPGA设计技巧(4):流水线(面积换取速度)

流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器,并暂存中间数据的方法。目的是将一个大 *** 作分解成若干的小 *** 作,每一步小 *** 作的时间较小,所以能提高频率,各小 *** 作能并行执行,所以能提高数据吞吐率(提高处理速度)。使用流水线一般是时序比较紧张,对电路工作频率较高的时候。典型情况如下:

1)功能模块之间的流水线,用乒乓 buffer 来交互数据。代价是增加了 memory 的数量,但是和获得的巨大性能提升相比,可以忽略不计。

2) I/O 瓶颈,比如某个运算需要输入 8 个数据,而 memroy 只能同时提供 2 个数据,如果通过适当划分运算步骤,使用流水线反而会减少面积。

3)片内SRAM的读 *** 作,因为SRAM的读 *** 作本身就是两极流水线,除非下一步 *** 作依赖读结果,否则使用流水线是自然而然的事情。

4)组合逻辑太长,比如(a+b)*c,那么在加法和乘法之间插入寄存器是比较稳妥的做法。

流水线优缺点

1)优点:流水线缩短了在一个时钟周期内给定信号必须通过的通路长度,增加了数据吞吐量,从而可以提高时钟频率,但也导致了数据的延时。

2) 缺点:功耗增加,面积增加,硬件复杂度增加,流水线就是插入寄存器,以面积换取速度。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)