介绍了FreeARM7 IP核的基本概况及其接口特点,以LPC2101为原型对该IP核进行了扩展。结合USB 1.1设备控制器IP核和自定制硬件逻辑,构建了一种微控制器功能验证回路。在主机端开发了验证程序、驱动和通信软件。验证程序下栽执行结果表明,功能验证回路工作正常,微处理器运行稳定。

1 FreeARM7 IP核简介

FreeARM微处理器的ARM7系列(简称FreeARM7)首发于www.socvista.com,由Free-arm联合其他ARM爱好者基于ARMv4架构开发而成。整个IP核代码采用可综合的Verilog HDL描述,接口简单,描述精炼,全部代码不超过2000行。在整体设计上,采用了三级流水线和哈佛结构,全面兼容各种中断和 *** 作指令(除Thumb和协处理器指令)。经过评估可知,该IP核基于FPGA和SMIC工艺库都有很好的实现结果。

FreeARM7接口定义如表1所列,概括起来可分为4类:

◆系统接口,提供系统控制信号;

◆中断源,提供ARM架构需要的5个中断信号;

◆ROM接口,与提供指令的ROM之间的接口;

◆单口RAM接口,与单口RAM和外设之间数据交互的接口。

其中,单口RAM接口可以实现两类用途:一、挂接单口RAM,使得FreeARM7能够正确地读写数据;二、挂接外设,使得FteeARM7能够正确 *** 作外设。

2 微处理器改进与逻辑扩展

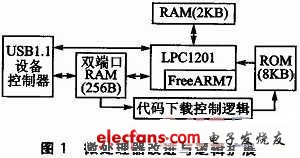

基于FreeARM7的微处理器改进与逻辑扩展的结构如图1所示。预期的实现目标是:在主机上编写嵌入式程序汇编成机器码后,经过USB 1.1设备控制器传输至双端口RAM中,在微处理器代码下载模式下,代码下载控制逻辑将双端口RAM中的机器代码装载至ROM中,之后启动微处理器正常工作模式,微处理器执行ROM中的嵌入式代码,接收主机通过USB传送来的参数值,并将运行结果通过USB返回至主机。

基于Cyclone II FPGA具体实现时,ROM、RAM和双端口RAM都是利用Quartus II软件中MegaWizardPlug-In.Manager工具例化相应的存储模块,而其他硬件逻辑的扩展都是以IP核(Verilog描述)的形式出现。

2.1 微处理器lP核改进

FreeARM7 IP核是微处理器的核心部分,不能直接作为微处理器使用,其原因是数据总线需要读取ROM内的数据、本文选择Philips公司32位ARM7微处理器LPC2101作为原型设计。LPC2101带有适当的存储资源,内嵌2 KB片内静态RAM和8 KB的Flash存储器,且软件可移植性好,工作可靠。参考LPC2101工作原理,当FreeARM7的输出信号ram_addr的最高4位为4'b0时,表示数据总线需要读取ROM的数据。为解决该问题,新增一个wrap文件lpc2101_arm.v完成该功能。它的作用是:当ram_addr[31:28]==4'b0时,该逻辑直接从rom_en、rom_addr、rom_data的接口中读取ROM数据,送入ram rdata。

2.2 USB1.1设备控制器

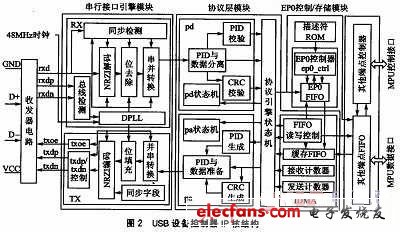

本文选用的USB设备控制器是课题组早期项目之一,它是由Opencores网站提供的初级开源版本改进而成,其结构如图2所示。IP核支持低速和全速模式,共有1个控制传输端点(EP0)、7个其他可配置端点,且缺少微处理器也能响应主机对设备的枚举。收发器电路主要完成模/数信号转换,即在OUT事物中将模拟信号D+和D-转换成串行接口引擎模块可识别的数字信号rxd、rxdp和rxdn,在IN事物中将数字信号txdp和txdn在使能信号txoe的控制下转换成模拟信号D+和D-;串行接口引擎模块主要完成收发包,根据传输方向可分为接收和发送,主要包括总线检测、同步检测、时钟恢复、不归零反向编码和解码、位填充及位去除、数据的串/并转换;协议层包括协议引擎态机、组包、解包、FIFO控制器;端点O控制器主要负责响应主机标准请求;描述符RAM存储了设备的各种描述符;其他端点控制器及FIFO提供了配置接口,目的是预留给开发者进行IP核移植。

2.3 代码下载控制逻辑

该逻辑主要功能是在代码下载模式下,将双端口RAM中的汇编程序转移到ROM中,其主要任务是产生读双端口RAM使能信号和地址信号,以及写ROM的使能信号和地址信号。在硬件逻辑中通过计数器实现。当系统复位或退出代码下载模式时,计数器:rom_wr_cnt清零,否则当USB接收完一个包(64字节)后,置计数器使能信号cnt_vld有效,rom_wr_cnt开始计数。cnt_vld直接作为读双端口RAM的使能信号,cnt_vld两级缓存后作为写ROM的使能信号。同时,rom_wr_cnt的低8位直接作为读双端口RAM的地址信号,rom_wr_cnt计算结果经过两级缓存后作为写ROM的地址信号。当64字节转移完毕后,置cnt_vld无效,此时rom_wr_cnt锁存当前值,等待下一个包接收完毕后再次置cnt_vld有效,代码下载控制逻辑就将下一个包的数据追加到ROM中,反复进行就完成了代码经由USB接口下载至ROM中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)