随着半导体技术,特别是 FPGA 的发展,单片芯片的处理能力越来越强。现在单片的处理能力都在 1Tbit 以上。而要处理这么多的数据,单靠原来的 LVDS, LVPECL 已经无法满足芯片接口吞吐量的要求。所以,如今越来越多的应用都用到高速 SERDES。

XILINX 的 SERDES 作为业界翘楚,越来越多地被客户接受并广泛应用。而随之而来设计、调试问题,也是让客户感到害怕的问题。特别是客户容易对高速 SERDES 犯怵,碰到问题又无从着手,导致进度受阻,压力倍增。

这是我着手总结 SERDES 设计调试的初衷。

这次主要讲 SERDES 复位设计。

复位的作用

众所周知,现在主流的 FPGA 上实现的都是时序逻辑。时序逻辑有一个特点就是前面的状态会影响到后面的状态。所以在这种应用里,初始状态的确定是整个设计里非常重要的一个环节。复位就是用来初始化逻辑状态用的。

对于 SERDES,根据不同的应用,其时钟方案是不同的。对此,SERDES 的状态,特别是BUFFER 的状态会受到很大的影响。由于 BUFFER 的读写时钟有效稳定的时间不同,大致会引起以下 2 种情况:

1. BUFFER 上下溢出,使得输入输出误码;

2. 多通道应用里,通道间引入偏移,使得各路通道绑定失败。

所以复位设计必须小心,特别需要和时钟方案相匹配,才能给可靠的设计打下良好的基础。

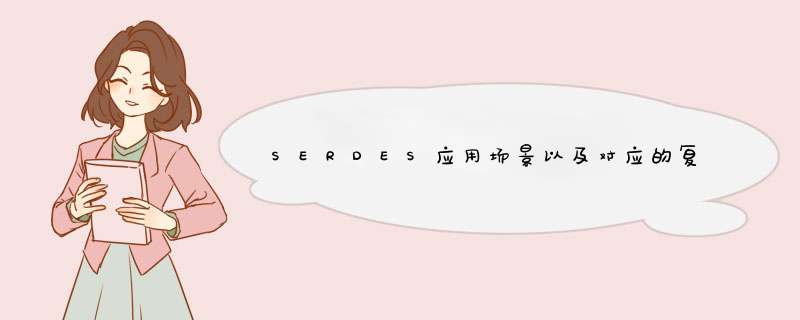

7 系列 GTX 的时钟结构

上面说到,复位应该和时钟方案相匹配,所以在这里简单介绍一下 7 系列 GTX/GTH 的时钟结构。

7 系列 SERDES 是以 QUAD 为单位的。在一个 QUAD 里,有

a) GTX/GTH: 一个 QUAD 里有 4 个 SERDES;

b) 2 个参考钟:它们可以连到任意一个 PLL 上。而且可以给上下相邻的 QUAD 提供参考钟;

c) CPLL:这是每路 GTX/GTH 都有的 PLL。这个 C 是指 Channel;

d) QPLL:每个 QUAD 内的 SERDES 共享的 PLL。这个 Q 是指 QUAD。

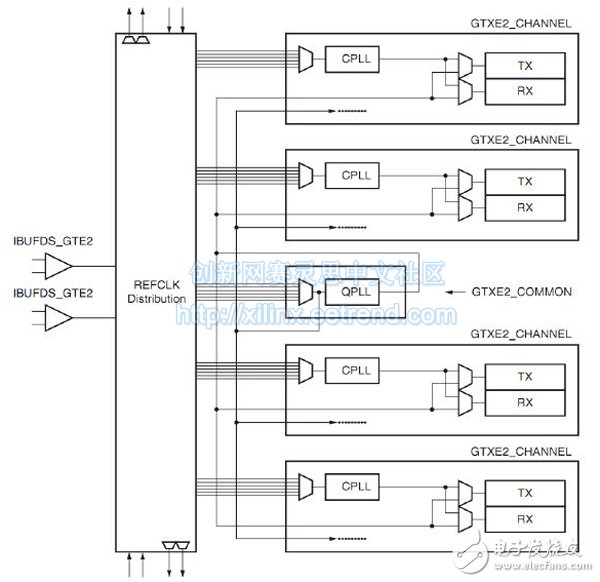

QPLL 和 CPLL 可以供到每个 SERDES 的发(TX)和收(RX)。在 SERDES 里有TX/RXSYSCLKSEL[1:0]端口选择使用哪个时钟源。

复位设计的案例

下面,根据不同的时钟方案,会列出一些复位的方法。

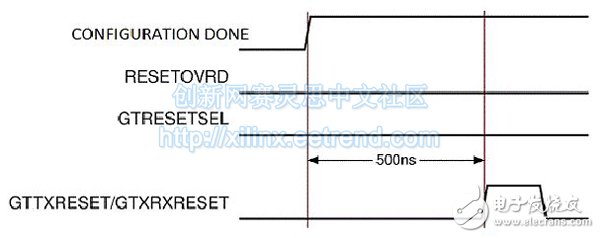

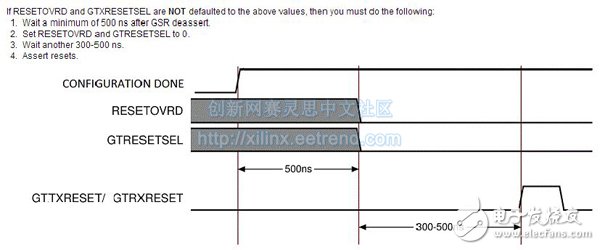

首先需要提醒的一点是:对于 7 系列的 SERDES, bit 文件下载完(CONFIGDONE 拉高)后的500ns 时间内的复位是无效的。SERDES 需要的复位是脉冲。所以 FPGA 配置完成后 500ns 后复位信号才能拉高。

如果在 500ns 之前就拉高,那是无效的。需要在后面在有一个正脉冲才行。

关于这个问题,在 XINLIX 官网上有 AR43482 作说明。

另外相对于以前的 SERDES,在 7 系列 SERDES 里多了 2 个信号:TXUSERRDY 和 RXUSERRDY。

这 2 个信号是用来控制何时进行 PCS 复位的。

SERDES 的顺序复位是指 GTXTXRESET 或 GTXRXRESET 有复位脉冲时,SERDES 会进行从 PMA一直到 PCS 的复位,最后把 TXRESETDONE 或 RXRESETDONE 拉高。

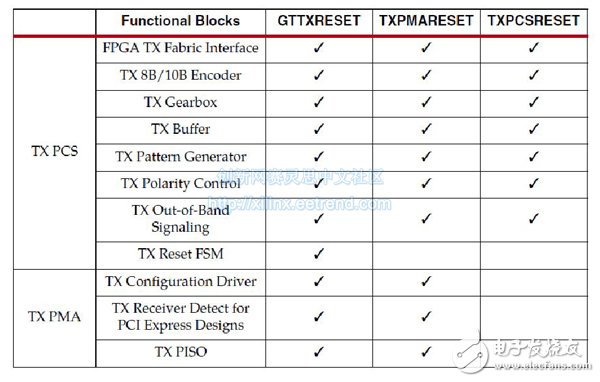

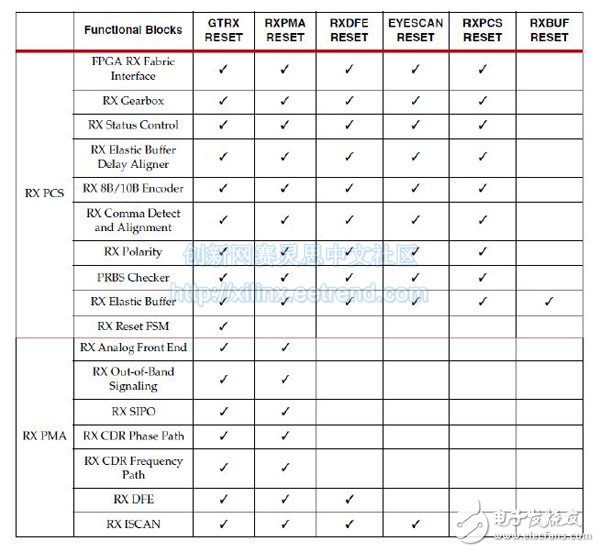

PMA 和 PCS 复位涵盖的范围见下表

整个复位顺序都是从 PMA 到 PCS 的。具体流程可以参考 UG476。

在完成 PMA 复位后进入 PCS 复位是,TXUSERRDY 和 RXUSERRDY 就是开关。只有当它们为高时才能进入 PCS 复位,继而完成整个 SERDES 的复位。TXUSERRDY 和 RXUSERRDY 的含义是用户钟 TXUSRCLK/TXUSRCLK2 和RXUSRCLK/RXUSRCLK2 都稳定了。这个时候可以进行 PCS复位了。

TX 复位案例

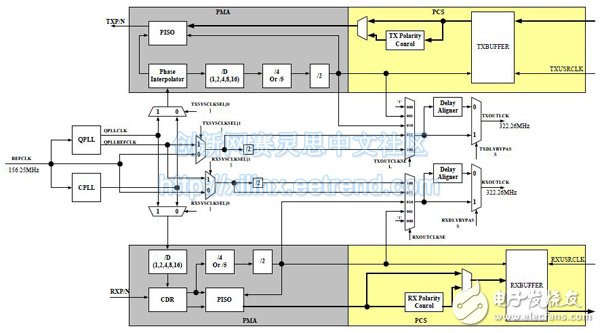

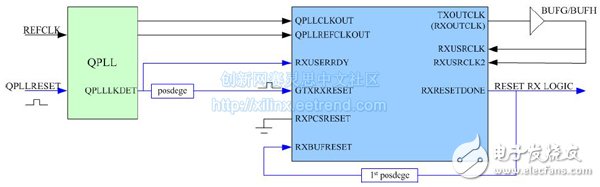

一、 TXOUTCLKSEL = TXOUTCLKPMA

这种情形下,TXOUTCLK 的频率是(LINE RATE)/(INTERNAL DATAWIDHT),它会随着线速度的变化而变化。

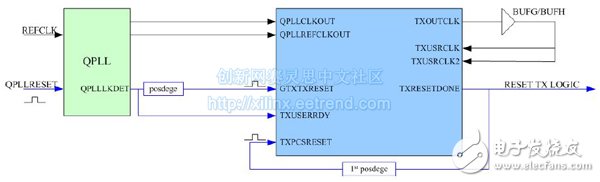

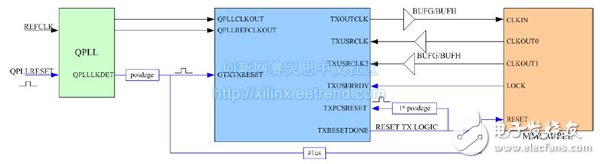

对于 7 系列 SERDES,内部位宽可以有 16/20 bit (即 2 字节)和 32/40bit(即 4 字节)2中选择。跟逻辑接口的外部位宽有 2、4、8 字节 3 种选择。由于逻辑可以跑到 368MHz以上。所以对于大多数的应用,TXUSRCLK/TXUSRCLK2 是可以同频的。此时,其时钟框图就会如下:

这种复位方案里,有一些要求:

? SERDES 工作在顺序复位模式下(工具产生的代码默认模式)

? RESETOVRD = 1’b0

? GTRESETSEL = 1’b0

? QPLLRESET 或 CPLLRESET 需要脉冲复位

? 至少一个参考钟周期

? QPLLLKDET 或 CPLLLKDET 的上升沿上产生 GTXTXRESET 脉冲,启动 SERDES 进入顺序复位

? 同时,把 QPLLLKDET/CPLLLKDET 连到 TXUSERRDY

? 最好能延时 2~3us 以保证 TXOUTCLK 稳定。

? 在 TXRESETDONE 的第一个上升沿做 TXPCSRESET 的复位

? 对单路应用不需要这个复位。

? 对于多路需要对齐输出的应用,需要把所有 TXRESETDONE 都拉高后做TXPCSRESET 复位以减少各路的输出偏移

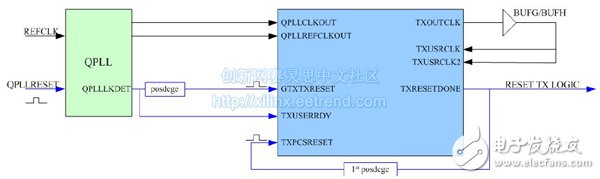

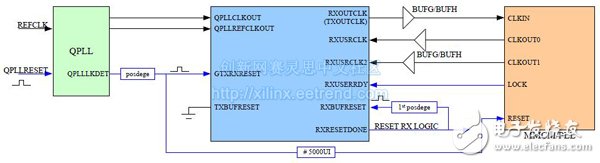

二、TXOUTCLKSEL = TXOUTCLKPMA,用到 MMCM

这个和上面一个的差别就是需要用到 MMCM。由于 MMCM 的输入是 TXOUTCLK,必须等到 TXOUTCLK 稳定后才能释放复位;而 MMCM 给 SERDES 提供 TXUSRCLK 和TXUSRCLK2,所以 TXUSERRDY 必须在 MMCM 稳定后才能拉高。

同样,对于多通道应用,需要在所有 TXRESETDONE拉高后给一个 TXPCSRESET 脉冲,这样可以减少发送数据通道间的偏移。

三、TXOUTCLKSEL = TXPLLREFCLK_DIV1/2

这种应用和第一种不同之处在于TXOUTCLK的时钟来源不同,这里是来自于参考钟。所以它会在 QPLL 锁定之前就稳定下来。当然我们还是可以借用第一种复位方法。只是QPLLLKDET/CPLLLKDET 送到 TXUSERRDY 时不需要延时去等待内部时钟稳定。

四、TXOUTCLKSEL = TXPLLREFCLK_DIV1/2,用到 MMCM同样,这种应用可以参考第二种。

当然由于 MMCM 的输入时钟是参考钟,所以它的复位释放也不需要等待 PLL 锁定。所以我们也可以用下面的复位方法

当然由于 MMCM 复位要求,QPLLRESET/CPLLRESET 的脉宽需要大于 3 个参考钟周期。

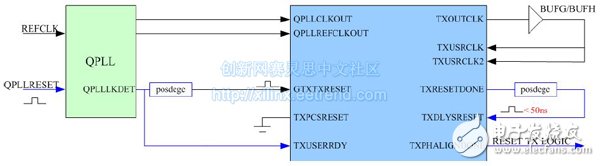

五、TXBUFFER BYPASS 情形

对于 CPRI 等有延时精度要求的应用,需要把 TXBUFFER 旁路。这时需要在上面的复位之外还要有相位对齐电路的复位。

要能进行相位对齐,对时钟有一定要求:

1. 同源同频。这里只是做相位对齐,频率必须相同;

2. 时钟稳定。只有时钟稳定后才能进行相位对齐 *** 作。

所以相对于前面使能 TXBUFFER 的应用的复位,在 TXRESETDONE 拉高后,做一次相位对齐 *** 作就可以了。

这里需要注意的一点是,TXDLYSRESET 的脉宽必须小于 50ns。

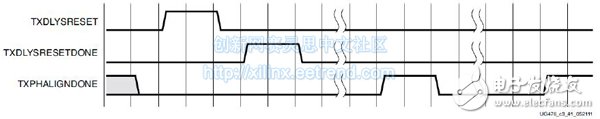

整个复位的波形图如下

和前面不同的是,这里用 TXPHALIGNDONE 作为后续逻辑的复位信号。这是因为这个信号拉高了,表示 SERDES 的初始化已经完成,可以工作了。而前面的几种应用,TXRESETDONE 的拉高是 SERDES 能够正常发送数据的标志。

RX 复位设计

这里只包括用到 RXOUTCLK 时的复位。如果是用 TXOUTCLK 作为 RXUSRCLK/RXUSRCLK2时钟源的情形,可以参考 TX 复位设计部分。

RX 的结构比 TX 要复杂。相对应的复位也会复杂一些。主要原因是 RXOUTCLK 的源头可能是 CDR 送出的恢复钟。也就是说,需要 CDR 稳定工作后才能有稳定的 RXOUTCLK 输出。所以后续的复位需要与此相配。

CDR 在有信号送入时,会跟踪上输入信号的频率、相位;当没有信号送入时,它会慢慢锁到本地时钟上,直到又有信号送入。这个不是跃变的过程,而是慢慢变化的。这里不会引入恢复时钟的跳变。

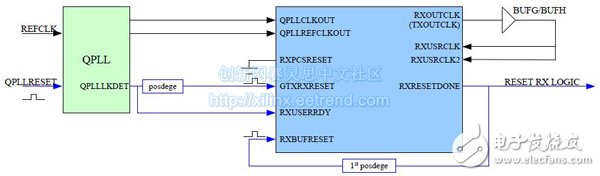

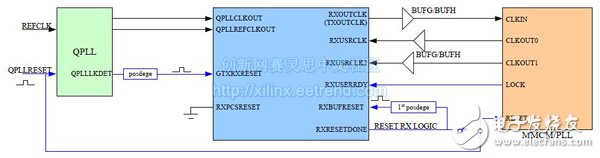

一、RXOUTCLKSEL = RXOUTCLKPMA

这种情形下,RXOUTCLK 的源头就是 CDR 的恢复钟。

由于初始化复位时,我们还是用 QPLLLKDET/CPLLLKDET 作为 RXUSERRDY 的输入,这样在 PLL 锁定后可以完成 PMA/PCS 的初始化。

但是在工作起来后,CDR 会锁到输入信号上。在跟踪过程中,恢复钟(也就是RXBUFFER 的写时钟)会有个渐变的过程。这个可能会导致 RXBUFFER 溢出。所以用RXBUFSTATUS[2]送到 RXBUFRESET。这样在 RXBUFFER 溢出时复位 RXBUFFER。

对于多通道应用,也是需要在所有 RXRESETDONE 都拉高时复位 RXBUFFRESET 一下,这样可以减少各路的偏移。当然,任意一路有前面说到的溢出,也需要复位所有的RXBUFFER。

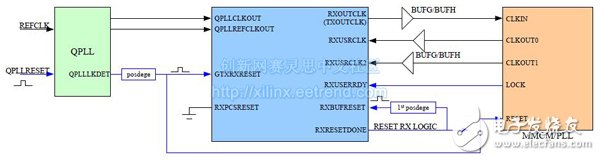

二、RXOUTCLKSEL = RXOUTCLKPMA,且用到 MMCM

这个情形下,我们需要注意的就是 MMCM/PLL 输入时钟源于 CDR 恢复时钟并给RXPCS 提供用户时钟。所以需要

1. MMCM 必须在 PLL 锁定后延时一段时间释放复位,这其中的时间就是 CDR 锁定的时间。

2. MMCM 的 LOCK 信 号 控 制 RXUSERRDY , 以 保 证 RXPCS 的 复 位 是 在RXUSRCLK/RXUSRCLK2 都稳定后释放的。

这种应用里,如果外部输入信号丢失,比如拔掉再插上光纤,那需要对接收侧做整体复位以保证接收的可靠。这时整个时钟都会重新复位一遍。

三、RXOUTCLKSEL = RXPLLREFCLK_DIV1/2

这种情形,RXUSRCLK/RXUSRCLK2 的源头都是参考钟,所以和 TXOUTCLKSEL = TXPLLREFCLKDIV1/2 的情形是一样的。在现实中会合并用 TXOUTCLK 来驱动 TXUSRCLK 和RXUSRCLK。

所以复位的方法参考 TX。

四、RXOUTCLKSEL = RXPLLREFCLK_DIV1/2, 且用到 MMCM

这 种 情 形 , RXUSRCLK/RXUSRCLK2 的 源 头 都 是 参 考 钟 , 所 以 和 TXOUTCLKSEL = TXPLLREFCLKDIV1/2 + MMCM 的情形是一样的。在现实中会合并用 TXOUTCLK 通过MMCM 来驱动 TXUSRCLK 和 RXUSRCLK。

所以复位的方法参考 TX。这里画出 2 中复位连接图:

五、RXBUFFER BYPASS

RXUBFFER BYPASS 模式下,由相位对齐电路实现 RXCLK 和 RXUSRCLK 的相位对齐。此时 RXUSRCLK 的源头必须来自 RXOUTCLKPMA, 而 RX_XCLK_SEL = RXUSR。

在大多数情况下,RX 工作在 SINGLE LANE 模式下。所以 RXPHASEALINGMENT 只要工作在 AUTO 模式下就可以了。

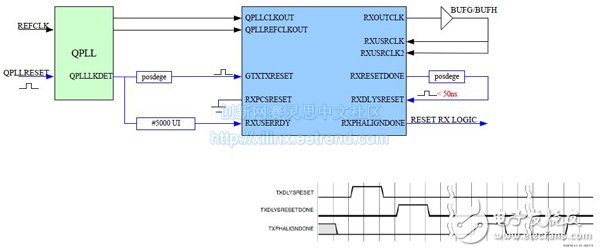

对于 GTX,RXPHASEALIGNMENT 的复位连接和波形如下:

RXPHALIGNDONE 作为 RX 逻辑的复位信号。

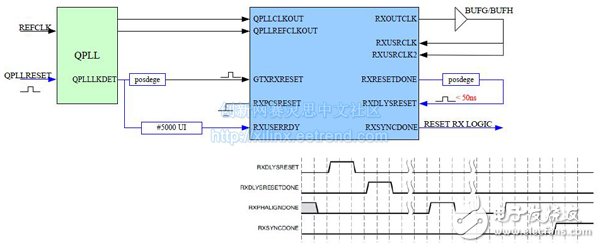

对于 GTH,RXPHASEALIGNMENT 的复位连接和波形如下:

RXSYNCDONE 作为 RX 逻辑的复位信号。

同样的要求:

1. RXDLYSRESET 的脉宽不能超过 50ns。

2. 相位对齐 *** 作必须在 RXRESETDONE 拉高后进行。

总结

对于时序系统,复位的设计会极大影响到系统的工作结果。对于 7 系列的 SERDES,其重要性是不言而喻的。这里列举的是一些应用场景以及对应的复位设计。希望对大家有帮助。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)