在22nm,或许是16nm节点,我们将需要全新的晶体管。而在这其中,争论的焦点在于究竟该采用哪一种技术。这场比赛将关乎到晶体管的重新定义。在22/20nm逻辑制程的开发中,业界都争先恐后地推出各种新的晶体管技术。英特尔三栅极(tri-gate)元件已取得重大进展。许多研究人员也正努力推动FinFET元件的研究工作。而包括ARM在内的多个主要的欧洲组织,以及美国的Globalfoundries则专注于研发完全耗尽型SOI (fully-depleted SOI, FDSOI)技术。不过,最近新创业者SuVolta和富士通也提出了另外一种崭新的选择。

晶体管设计会对所有下游的设计工作带来深远影响──从制程设计到物理设计都包括在内,其涵盖领域甚至包含了逻辑设计师在功率和时序收敛方面的权衡。

问题在哪里?

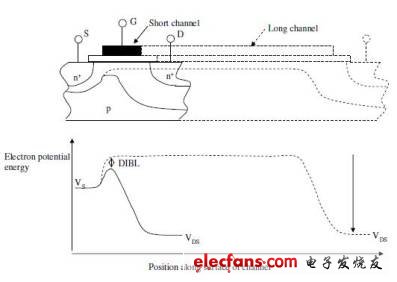

为何制程工程师们痛下决心革新晶体管设计?最简单的回答是短沟道效应。不断追逐摩尔定律(Moore‘s Law)的结果是MOSFET沟道长度不断缩减。这种收缩提高了晶体管密度,以及其他的固定因素和开关速度等。但问题是,缩短这些沟道却也带来了诸多严重问题。针对这些问题,我们可以简单地归纳为:当漏极愈接近源极,栅极便愈来愈难以夹断(pinch off)沟道电流(图1)。这将导致亚阈值漏电流。

图1:沟道上的栅极控制可消除短沟道效应

自90nm节点以来,这场对抗漏电流的战役已经持续许久。向全high-k/金属栅极(HKMG)的转移,让栅极能在不让漏电流失控的情况下更好地控制沟道电流。但到了22nm节点,许多人认为,平面MOSFET将输掉这场战役。目前还没有办法在足够的性能条件下提供良好的漏电流控制。“HKMG解决了栅极漏电流,”一位专家表示。“现在,我们必须解决沟道漏电流了。”

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)