脉冲宽度调制(Pulse Width ModulaTIon.PWM)控制技术以其控制简单、灵活和动态响应好的优点而成为电力电子技术和模拟信号数字传输通信领域最广泛应用的控制方式,因此研究基于PWM技术的脉冲宽度及周期可调的信号发生器具有十分重要的现实意义。

这篇文章主要就是说明计数器计算时钟脉冲的上升沿个数,再通过输出电平反复翻转得到计数个数(脉冲宽度)可控的PWM信号。

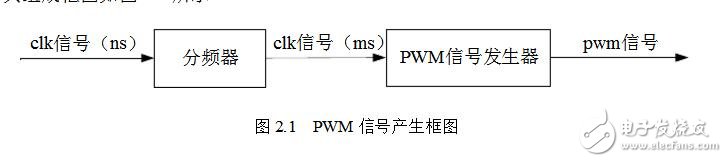

为了使本次设计产生的PWM信号能用于频率稳定度高的晶振,故在系统设计中添加了一个分频模块,因此PWM信号发生器由分频器和信号发生器两个部分组成。其组成框图如图2.1所示

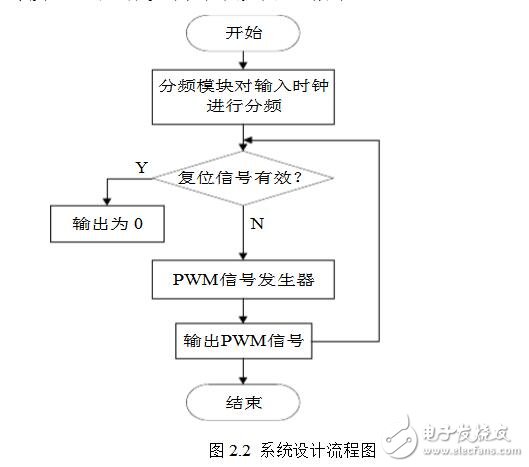

PWM信号发生器的总体设计流程图如图2.2所示

如上图的框图所示,输入是纳秒(ns)级的高频时钟信号,经过分频模块后产生毫秒(ms)级的低频时钟,然后由低频时钟控制信号发生器,产生一定周期的矩形波,再经过具体的设计形成占空比可调的PWM信号。

本次设计中,设计要求是产生1KHz的脉冲宽度可调的矩形信号,仿真中输入时钟clk的周期为10ns,经过1000分频器后变成周期为10us(频率为0.1MHz)的时钟,再通过信号发生器模块中的计数上限为100计数器,产生周期为1ms(频率为1KHz)的周期矩形信号,再有输入端口控制占空比,产生宽度可调的PWM信号,实现设计要求的功能。

分频实际就是一个计数的过程,通过计数个数来控制输出高低电平的时间,最重要的是高低电平的维持时间相等,即产生方波信号。

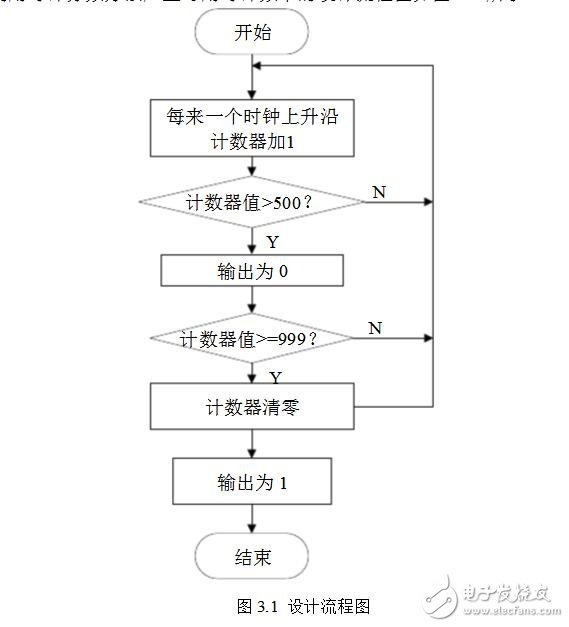

使用时钟分频方法产生可用时钟频率的设计流程图如图3.1所示:

if clkin=‘1’ and clkin‘event then --时钟上升沿触发

if count=1000 then count:=0; --计数计到999则清零

elsifcount《=500 then clkout《=‘1’; --计数到500电平翻转

elseclkout《=‘0’;

end if;

count:=count+1; --时钟上升沿计数

end if;

定义实体之后,在由输入时钟(ns)触发的进程中实现分频,首先定义一个中间计数变量,当计算输入时钟上升沿个数从0至500时输出高电平,从500至1000时输出低电平,从而产生周期为输入信号1000倍的方波信号,分频比可由下式得到:

A= To ÷TI (3.1)

其中,To为输出时钟的周期,TI为输入时钟的周期。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)