现代社会正向数字化、信息化方向高速发展,在这一过程中,往往需要高速信号的实时性数字化处理。例如,随着科技的进步,现代雷达等应用信号的数字化处理上有了长足的发展,但也带来了新的问题,这些应用的数字信号处理具有海量运行需求的应用背景,如巡航导d末制导雷达地形匹配、合成孔径雷达的成像处理、相控阵雷达的时空二维滤波处理等领域。目前,单片DSP难以胜任许多信号处理系统的要求。而常见的解决方案也是高速A/D采样与信号处理功能是在多块不同的板卡上实现,这给实际应用带来很多不便。

鉴于上述现有技术所存在的问题,本设计平台的目的是:

(1)实现高速中频信号(如雷达信号)的数字化处理并进行实时传输数据或进行数据的实时计算,并能通过输出电路进行结果显示;

(2)自定义控制总线可以实现对高速中频信号处理板进行灵活控制,具有较强的可配置性和丰富的灵活性;

(3)高速A/D采样与D/A回放及数据处理单元集成在一块板上,在集成度高的同时也降低了高速信号在传输过程中出现差错的概率。

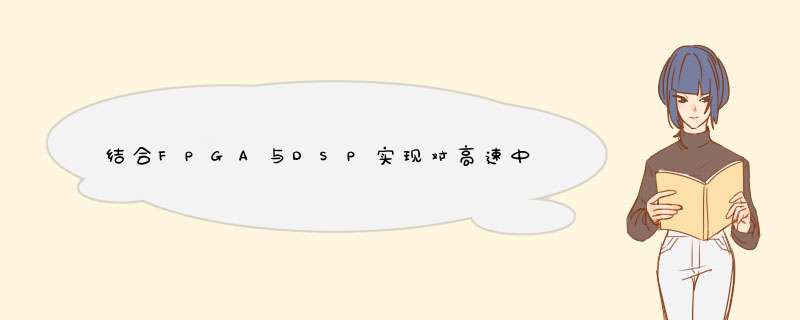

1 平台设计方案高速中频采样信号处理平台由主控制电路、高速A/D与D/A电路、信号处理单元电路、光纤通道电路、时钟管理电路、存储单元和外部接口电路组成,其总体框图如图1所示。

在实际应用过程中,四路A/D通道可以接收不同的信号源的信号,D/A通路可以对外进行数据显示等多种功能,时钟管理电路管理内外时钟的使用及对板上系统供给工作时钟,两路光纤通道可以与其他高速设备相连接,自定义总线可以与CPU或主控制器相连接对平台进行有效灵活的控制。

1.1 高速A/D与D/A设计

四路高速A/D采样通道采用两片NS公司的ADC081000实现,每片有两个A/D通道,相比多片A/D器件的通道间相位恒定设计是一个难点而言,单片A/D器件可以更容易实现两路通道间的相位恒定。ADC081000是一款高性能的A/D采集芯片,单通道8 b采样频率为1 GHz。本平台中A/D通道间采样数据的相位恒定是利用采样时钟相位间的恒定来实现的。在设计时,使时钟芯片到两片A/D器件间的时钟线等长,两片A /D器件到FPGA间的时钟线与数据线也分别等长,并且还利用一片FPGA设计了对两片A/D器件的软启动控制,这就更保证了四路通道间采样时钟的相位恒定。

两路高速D/A通道采用两片AD公司的AD9736实现,AD9736单通道14 b,采样频率可达1 200 MSPS。两路高速D/A通路也利用一片FPGA作控制,实现通道间相位差的恒定。

1.2 信号处理单元设计

信号处理单元包括FPGA和DSP两大部分。

FPGA部分主要由四片Virtex-4 SX55组成,四片FPGA间实现有串行连接和相隔间的连接。FPGA电路主要是实现对高速A/D采集数据的预处理和高速D/A回放数据处理,并且控制高速A/D电路采样时钟的相位恒定与高速D/A电路采样时钟的相位恒定,同时也根据需要与相应的DSP进行数据交换或传递。FPGA电路上连接的光接口电路也可以实现与其他系统进行高速、实时的数据交换。

A/D采样之后的数字信号速率非常高,要从这些高速信号中得到有用的基带信号,需要有效地对其进行数字下变频、抽取、滤波等处理,这些功能都可以通过FPGA来实现。FPGA具有较高的处理速度和较高的稳定性,同时又具有设计灵活、易于修改和维护的优点,可以适应不同系统的要求,提高了系统的适用性及可扩展性。

DSP电路是本平台信号处理的核心,完成大部分的数据处理工作,由四片ADSP TS201组成,四片DSP间实现了两两间的Link口互连,构成了分布式并行系统,可以把复杂的算法分割成小的任务给各处理器完成,从而减少任务的执行时间。

根据设计需要,平台数据的传输量很大,多DSP之间的数据传输速度尤为重要,采用Link口来传输数据,可以在不增加辅助电路的前提下,DSP间的直接互联。而且,基于Link口的数据传输采用专门的数据通道,不占有系统总线资源,消除了传输过程中的总线仲裁,减少了网络延迟带来的不确定因素。四片DSP间Link口的传递数据能力高达600 MB/s。

DSP主要是通过软件设计来实现数字基带信号处理以及比特流控制、编码解码等高速的数据交换和处理功能。对DSP开发的软件工具是ADI公司的VisualDSF++4.0,它是TIgerSHARC++系列DSP的集成开发环境,支持汇编语言、C语言、C++等开发语言,能让程序员使用这些工具编写出相对于特定DSP的高性能应用程序,发挥强大的处理能力。在本平台中,每片DSP的地位都是对等的,能够根据不同的要求,硬件结构不用改变,只须在DSP的软件算法中稍加改动,系统就能实现新的功能。

1.3 主控制电路设计

主控制电路与信号处理单元电路和外部接口电路相连,其核心是一片规模较小的FPGA。它主要是控制信号处理单元的同步复位及工作控制,可以将从外部主机接收到信号传递给信号处理单元,也可将信号处理单元的有关信息传递到外部主机中。

1.4 其他主要电路设计

时钟管理电路主要是负责板上FPGA、DSP、光口、高速A/D与D/A等正常工作所需要时钟生成与配置。外部存储电路是FPGA与DSP正常工作时所需要的外部RAM空间大小的设计。外部接口电路是本平台与其他设备进行连接的控制接口。光纤通道电路由两路光纤通道组成,每路可以工作在2.5 Gb/s,可以与其他系统进行数据交换。

2 性能测试决定平台性能的指标有多个,选取最主要的三个进行测试,结果如下。

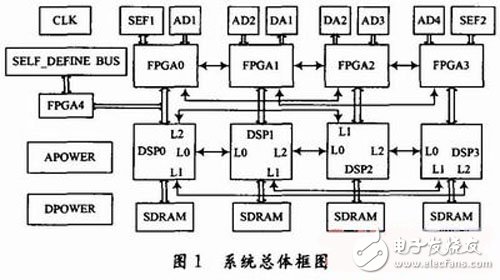

2.1 A/D采样的有效位数

有效位数是用来表述A/D器件的一项总体指标,对精确评价系统性能非常重要。对于A/D采样有效位的测试,采用A/D器件的最大量程输入,在FPGA中取得数据,用Matlab来对数据处理进行计算得到的。四路A/D采样通道有效位的测试数据如表1所示。

2.2 A/D通道间相位恒定

A/D通道间的相位恒定指标直接测试比较困难,在平台设计中已经保证了同一芯片两路A/D通道间的相位差是恒定的,只要测试两片A /D芯片输出时钟相位差是否恒定即可判定。表1中也显示了两片A/D器件输出时钟的相位差测试结果。

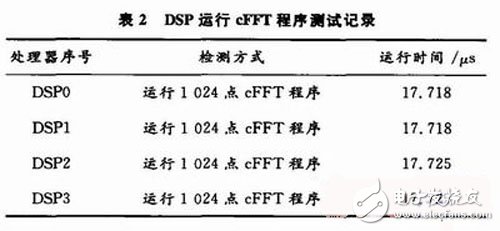

2.3 DSP运算速度

DSP的运算速度和精度决定着系统的数据处理能力,同时也会对整个系统的性能和结构产生重要的影响。DSP的处理能力可以用1 024点的复数FFT计算时间进行比较。Link口传递速度的测试,可以将Link口的工作时钟设定在600 MHz,按4 b进行数据传递,如果接收到数据没有错误,即可认定Link口的工作速率可以达到600 MB/s。经过测试,在工作频率为600 MHz,按4 b进行数据传递的情况下,各个Link均通过测试,也就是说每个Link口工作速率都可以达到600 MB/s。经过测试,平台上两个光口的传输速度均达到了2.5 Gb/s。DSP运算速度测试结果见表2。

通过上述测试结果可以看出,本平台设计合理,FPGA与DSP的结合使用,能充分发挥各自的优势,实现对高速、多路、海量信号的实时处理。另外,高度集成化设计,大大减少了平台所占用的空间体积,也使功耗大大减小。平台在兵器某所项目验证中,接入实际雷达信号进行测试,各项指标均达到了设计要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)